Preparation method of static random access memory

A static random access memory technology, applied in semiconductor/solid state device manufacturing, electric solid state devices, semiconductor devices, etc., can solve problems such as voltage mismatch of static random access memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

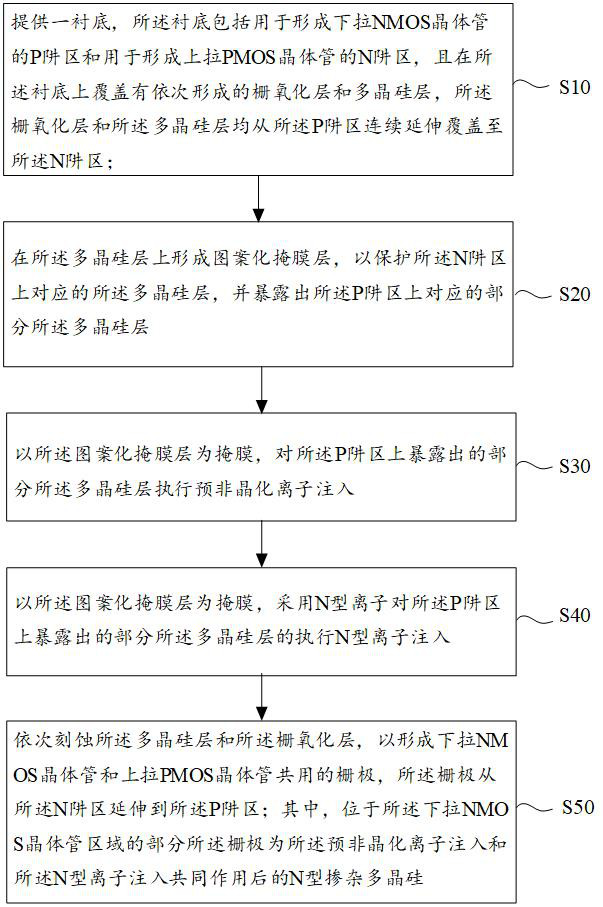

[0031] In order to solve the above technical problems, this embodiment provides a preparation method of SRAM, please refer to figure 2 , the preparation method of the SRAM comprises:

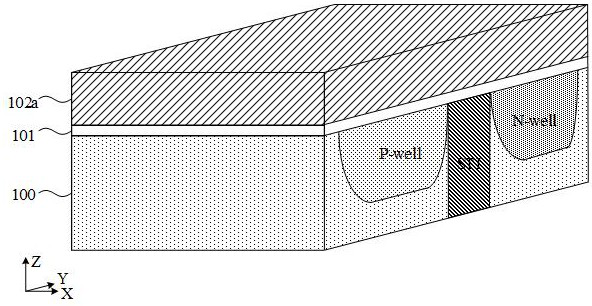

[0032] Step 1 S10: providing a substrate, the substrate includes a P well region for forming a pull-down NMOS transistor and an N well region for forming a pull-up PMOS transistor, and the substrate is covered with sequentially formed gates An oxide layer and a polysilicon layer, both of the gate oxide layer and the polysilicon layer continuously extend from the P well region to cover the N well region.

[0033] Step 2 S20: forming a patterned mask layer on the polysilicon layer to protect the corresponding polysilicon layer on the N well region and expose a corresponding part of the polysilicon layer on the P well region.

[0034] Step 3 S30: Using the patterned mask layer as a mask, performing pre-amorphization ion implantation on the exposed part of the polysilicon layer on the P well regio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com