Spherical grid array package

An array packaging and ball grid technology, which is applied in the direction of printed circuits, electrical components, and electrical solid devices connected with non-printed electrical components, and can solve problems such as limitations and difficulties in implementation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

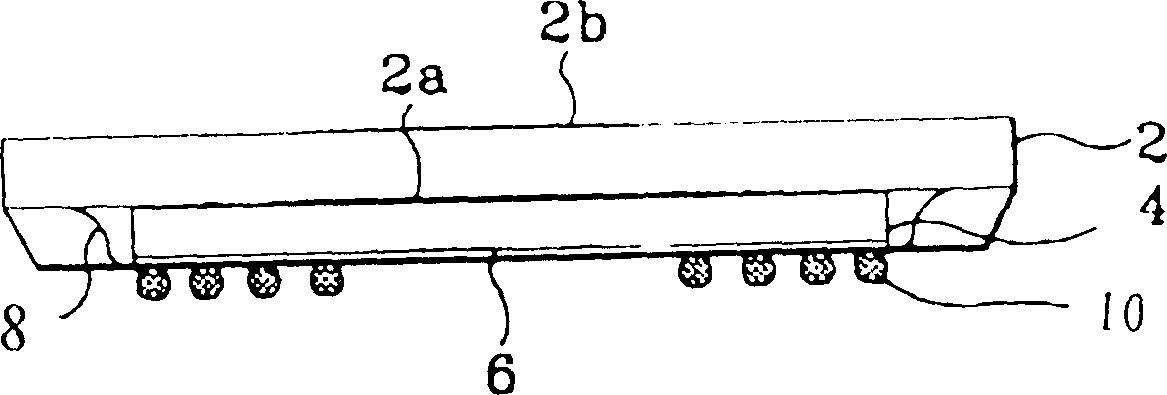

[0012] figure 1 It is a schematic cross-sectional view of a representative micro ball grid array (μ-Ball Grid Array: μ-BGA) in the conventional chip scale package (Chip Scale Package) group.

[0013] refer to figure 1 , a semiconductor chip 2 is provided, that is, a die, which has an inner surface 2a and an outer surface 2b, a plurality of semiconductor elements are formed on the inner surface 2a, and a plurality of semiconductor elements are formed on the upper surface of the inner surface 2a for communicating with the outside Bonding points (not shown) where the circuit passes signals. These bonding points are formed at the ends of the semiconductor chip 2 . exist figure 1 In this case, the inner surface 2a of the semiconductor chip 2 faces downward. On the inner surface 2a of the semiconductor chip 2, an elastic rubber 4 and a flexible beam lead film 6 printed with circuit wiring are laminated in this order. Next, the elastic rubber 4 and the beam lead film 6 will be d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com