A strain purified silicon substrate for semiconductor quantum computation and forming method thereof

A quantum computing, silicon substrate technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of high impact, low electron mobility of purified silicon, etc., to improve quality, great research significance and economic benefits , the effect of reducing the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

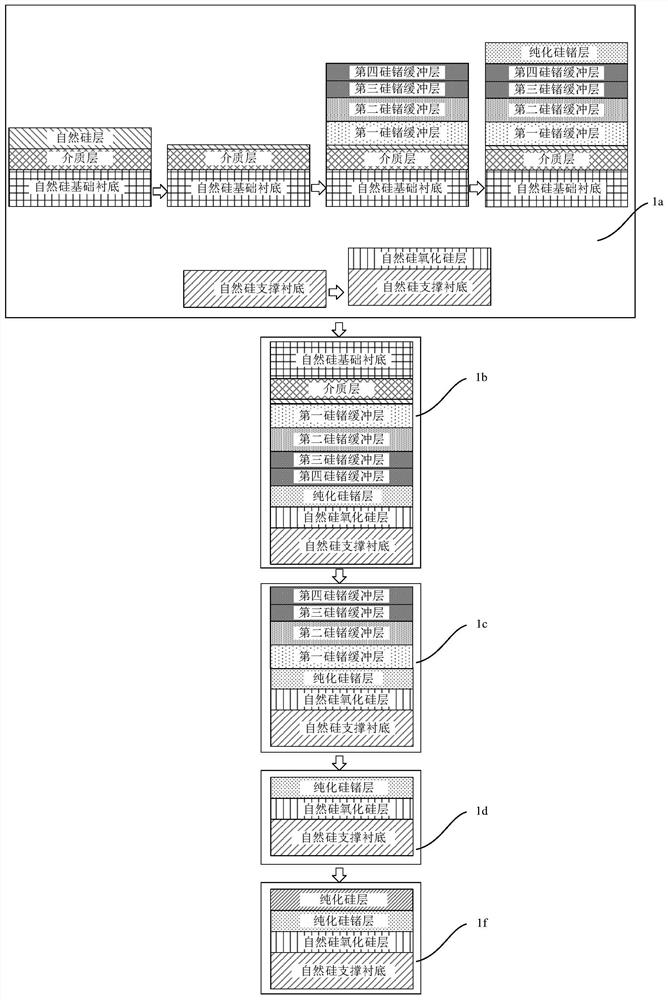

[0093] The purified silicon-germanium substrate of this embodiment includes a natural silicon support substrate, a natural silicon oxide layer and a purified silicon-germanium layer stacked in sequence, see figure 1 , the specific formation method includes the following steps:

[0094] Step 1a: Provide a base substrate, thin the natural silicon layer in the base substrate, so that the thickness of the thinned natural silicon layer is less than 20nm, and epitaxially form multiple layers of silicon germanium on the thinned natural silicon layer A buffer layer, epitaxially forming a purified silicon germanium layer on the silicon germanium buffer layer located on the surface, to obtain a donor substrate;

[0095] A natural silicon support substrate is provided, and a layer of natural silicon oxide layer is formed on the natural silicon support substrate;

[0096] Step 1b: pressure bonding the donor substrate to the native silicon support substrate, both the base substrate and th...

Embodiment 2

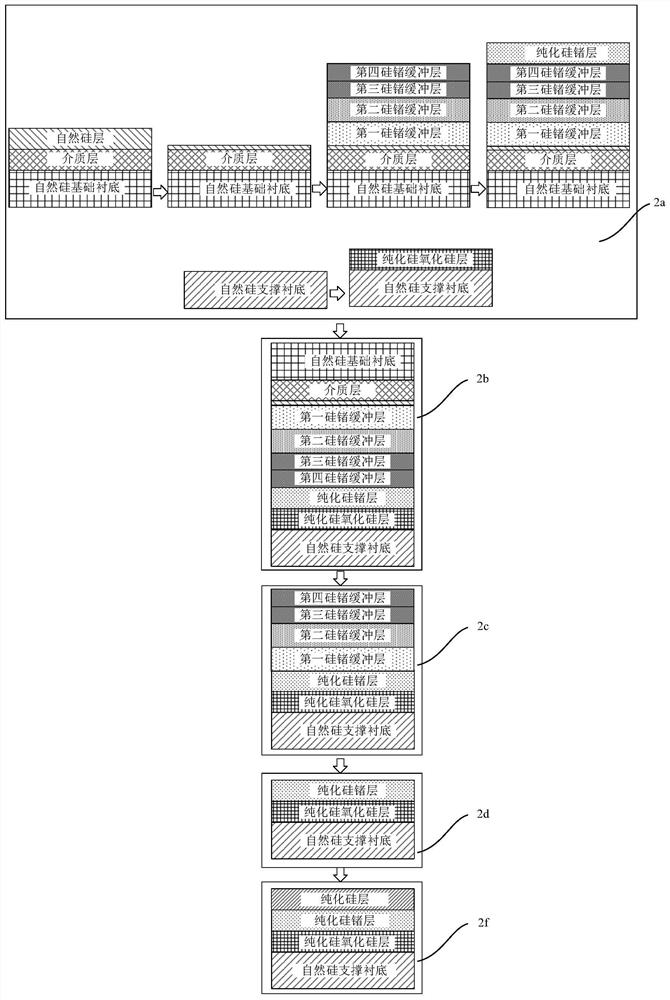

[0101] The purified silicon germanium substrate of this embodiment comprises a natural silicon support substrate, a purified silicon oxide layer and a purified silicon germanium layer stacked in sequence, see figure 2 , the specific formation method includes the following steps:

[0102] Step 2a: Provide a base substrate, thin the natural silicon layer in the base substrate so that the thickness of the thinned natural silicon layer is less than 20nm, and epitaxially form multiple layers of silicon germanium on the thinned natural silicon layer A buffer layer, epitaxially forming a purified silicon germanium layer on the silicon germanium buffer layer located on the surface, to obtain a donor substrate;

[0103] Provide a natural silicon support substrate, and form a layer of pure silicon silicon oxide layer on the natural silicon support substrate;

[0104] Step 2b: pressure bonding the donor substrate to the native silicon support substrate, both the base substrate and the ...

Embodiment 3

[0109] The purified silicon-germanium substrate in this embodiment has the same structure as the purified silicon-germanium substrate provided in Embodiment 1, including a natural silicon support substrate, a natural silicon oxide layer and a purified silicon-germanium layer stacked in sequence, see image 3 , the specific formation method includes the following steps:

[0110] Step 3a: Provide a base substrate, thin the natural silicon layer in the base substrate, so that the thickness of the thinned natural silicon layer is less than 20nm, and epitaxially form multiple layers of silicon germanium on the thinned natural silicon layer A buffer layer, epitaxially forming a purified silicon germanium layer on the silicon germanium buffer layer located on the surface, and forming a layer of natural silicon oxide silicon layer on the purified silicon germanium layer to obtain a donor substrate;

[0111] providing a native silicon support substrate;

[0112] Step 3b: Diffusion bon...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com