Multi-stage temperature detection circuit and temperature detection method

A temperature detection circuit, multi-stage technology, applied in thermometers, thermometers with directly sensitive electrical/magnetic components, measuring devices, etc., to achieve the effect of simplified structure, low power consumption design, and improved integration.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

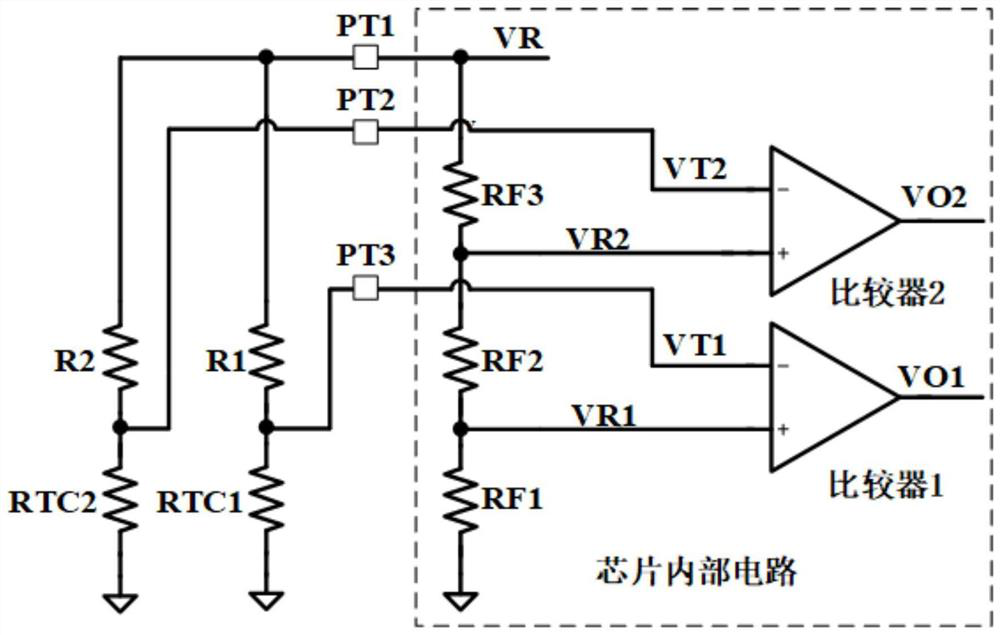

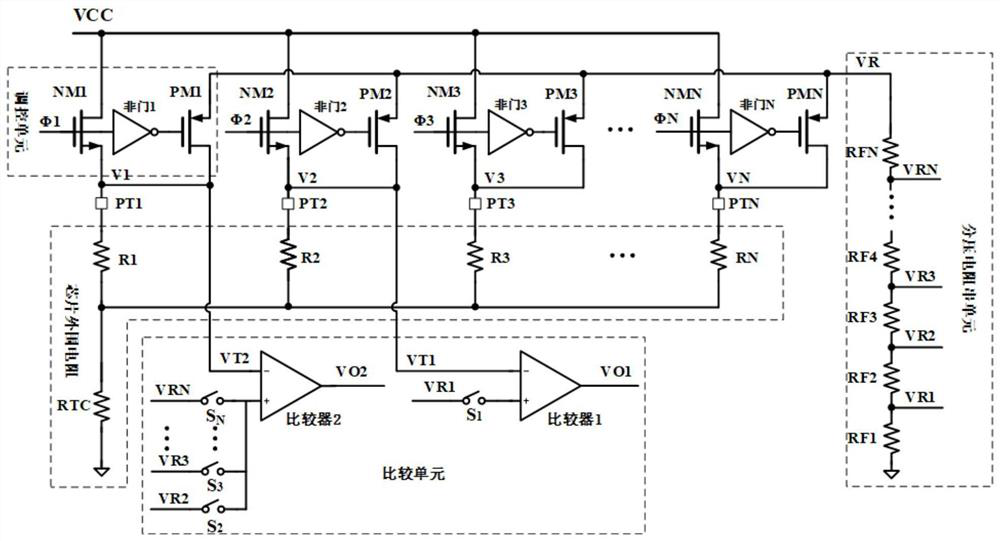

[0060] Such as figure 2 As shown in the present embodiment, the multi-stage temperature detecting circuit includes an internal circuit and a peripheral circuit, and the internal circuit is integrated into the integrated circuit of the control chip, and the internal circuit includes n NMOS tube: Nm1-NMN, N PMOS tube: PM1-PMN, N non-door: Non-door 1-non-door N, sequentially connected N RF resistance: RF1-RFN, 2 comparators: comparator 1 and comparator 2, where N is Gady greater than or equal to 2; the peripheral circuit includes a resistor R1-Rn and a thermistor RTC, and the threshold value of each temperature point can be adjusted by independently adjusting the resistance of the partial voltage resistor in series.

[0061] Specifically, the gate ends of the N NMOS tube NM1-NMN are connected to the gate control signal φ1-φn, respectively, and are connected to the input of the non-door 1-non-gate N; NMOS tube NM1-NMN, the drain end and join To the power supply VCC terminal; the sour...

Embodiment 2

[0066] Combine figure 2 3, the VCC provides power supply for the chip, and the specific operation of the multi-stage temperature detecting circuit of the present embodiment is as follows:

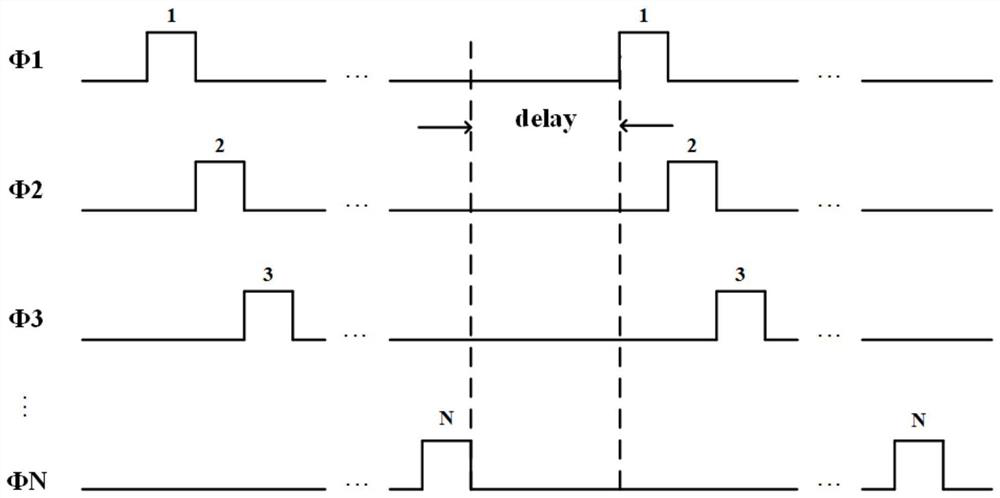

[0067] When the gate control signal φ1 is high, the remaining gate control signal φi other than φ1 is low, the NMOS tube Nm1 is turned on, and the high-level gate control signal φ1 passes through the non-door 1 to low power. Flat, the PMOS pipe PM1 is turned on, and the gate control signal φ1 is turned on the switch S1, and the switch S1 is closed when the switch S1 is high. The source voltage of the NMOS tube NM1 is a voltage value after the gate control signal φ1 is high, that is, the voltage V1, and the source drain voltage of the PMOS pipe PM1, that is, VR = V1. After the voltage Vr is resistant to the resistor network, according to the series resistance division pressure, the voltage value of the positive phase input end of the comparator 1 can be obtained:

[0068]

[0069] That is, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com