Heterogeneous many-core-oriented data transmission method based on space rearrangement

A data transmission method and data transmission technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of insufficient use of data transmission bandwidth, excessive data transmission startup overhead, lower data transmission efficiency, etc., and improve memory access efficiency. and overall performance, reduced times and startup overhead, ease of use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

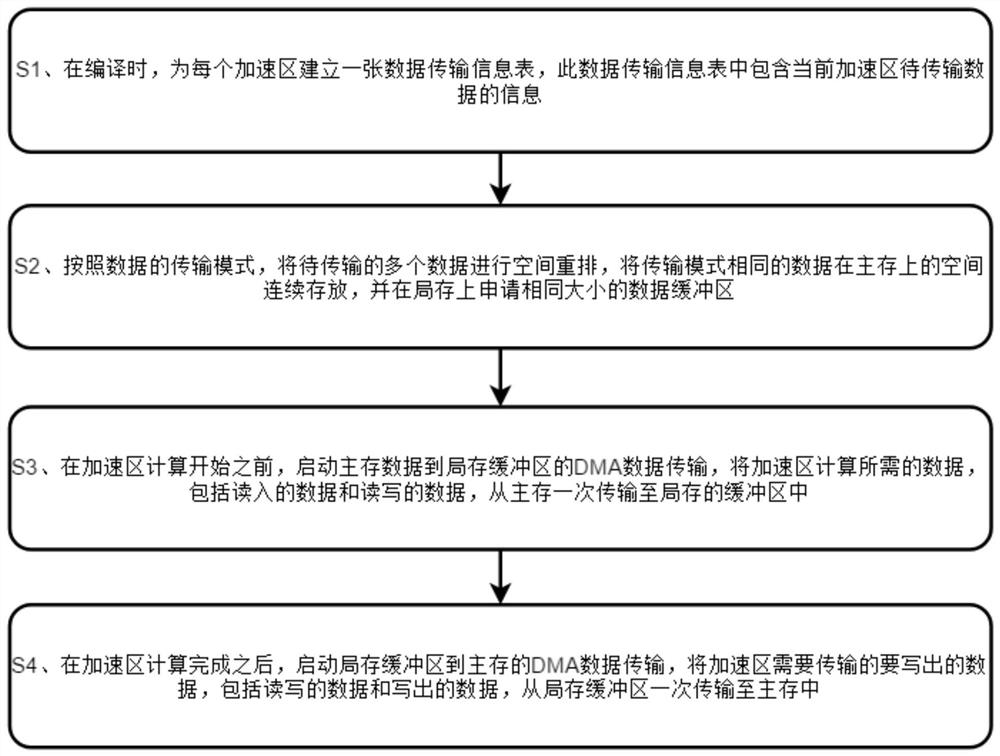

[0018] Embodiment: a data transmission method based on spatial rearrangement for heterogeneous many cores, based on a large-scale heterogeneous system, comprising the following steps:

[0019] S1. When compiling, create a data transmission information table for each acceleration area. This data transmission information table contains the information of the data to be transmitted in the current acceleration area. The information of the data to be transmitted includes the storage address of the data in the memory, The variable name, data length and data transmission mode corresponding to the data in the program;

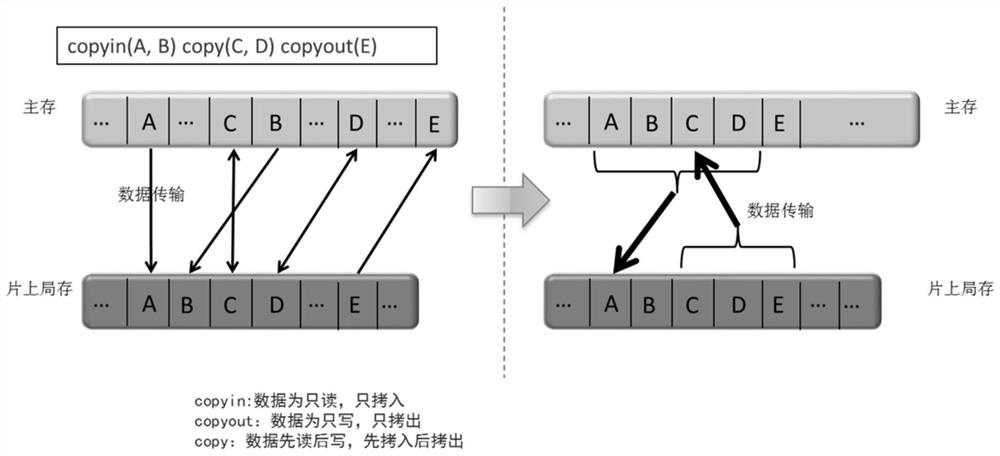

[0020] S2. According to the data transmission mode, rearrange the space of multiple data to be transmitted, store the data with the same transmission mode in the space on the main memory continuously, and apply for a data buffer of the same size on the local memory;

[0021] S3. Before the acceleration area calculation starts, start the DMA data transmission from the m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com