Chip synchronous testing device and chip synchronous testing method

A technology of synchronous testing and chip testing, which is applied in the directions of measuring devices, electronic circuit testing, measuring electricity, etc., can solve the problem of inability to synchronously test multiple chips, and achieves the solution of inability to synchronously test multiple chips, and realizes the diversity of types and chips. The effect of improving test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

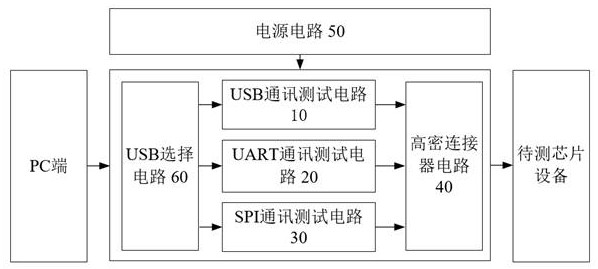

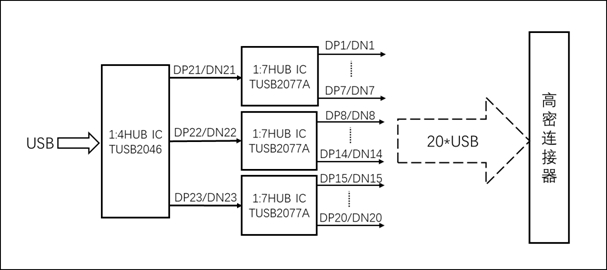

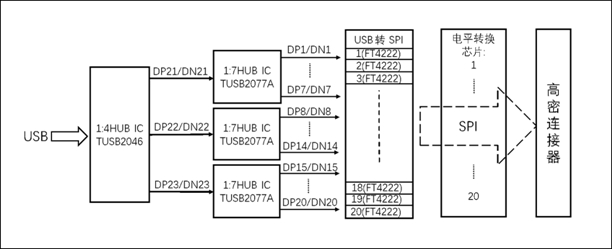

[0026] figure 1 It is a structural diagram of a chip synchronization testing device provided by an embodiment of the present invention. Such as figure 1 As shown, the embodiment of the present invention provides a device capable of realizing multi-chip synchronous testing, the device includes: a communication testing circuit, including a plurality of communication line ports, used for synchronous testing of multiple chips; a high-density connector circuit 40, It is used for the connection between the communication test circuit and the chip device under test. Wherein, described communication test circuit comprises: USB communication test circuit 10, is used fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com