Nanosheet field effect transistor and preparation method thereof

A field effect transistor and nanosheet technology, applied in the field of nanosheet field effect transistors and their preparation, can solve problems such as nanosheet damage, and achieve the effects of increasing protection, reducing gate delay effect and increasing stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

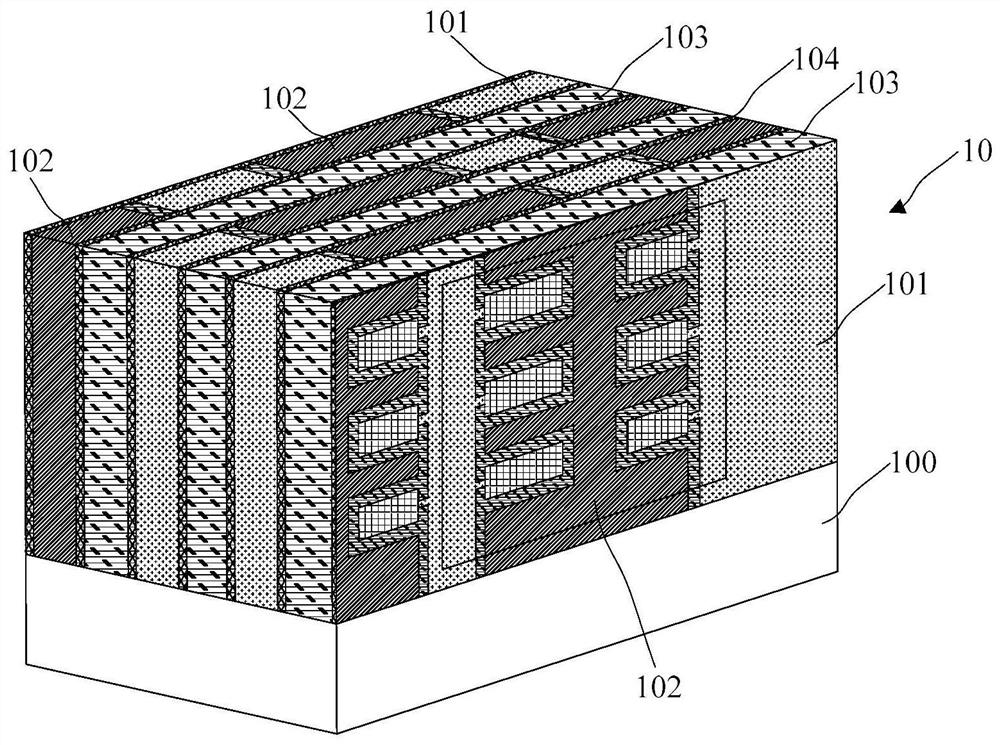

[0082] This embodiment provides a nanosheet field effect transistor, such as figure 1 As shown, the field effect transistor 10 includes a semiconductor substrate 100, and the semiconductor substrate 100 may be any semiconductor substrate commonly used in the field, such as a silicon substrate.

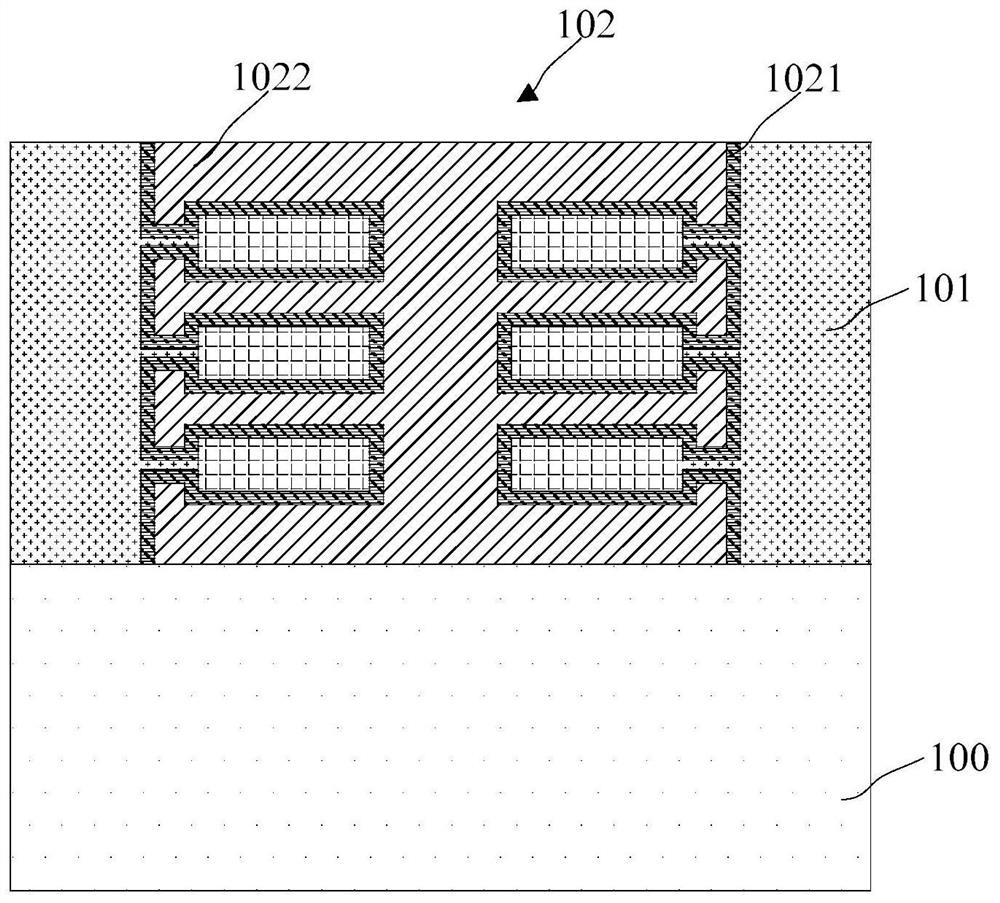

[0083] Insulation and isolation structures 110 are formed on the semiconductor substrate 100, and stacked multilayer nanosheets 105 are formed between the isolation and isolation structures 110, and the multilayer nanosheets 105 are spaced apart from each other. Such as figure 2 As shown, the stacked nanosheets 105 form a channel region. In this embodiment, an insulating isolation structure support portion 111 supporting the nanosheet 105 is formed between the nanosheet 105 and the insulating isolation structure 101 (see the attached Figure 10 ).

[0084] Such as figure 1 As shown, the nanosheet field effect transistor also has a gate structure 102 . The gate structure 102 is fo...

Embodiment 2

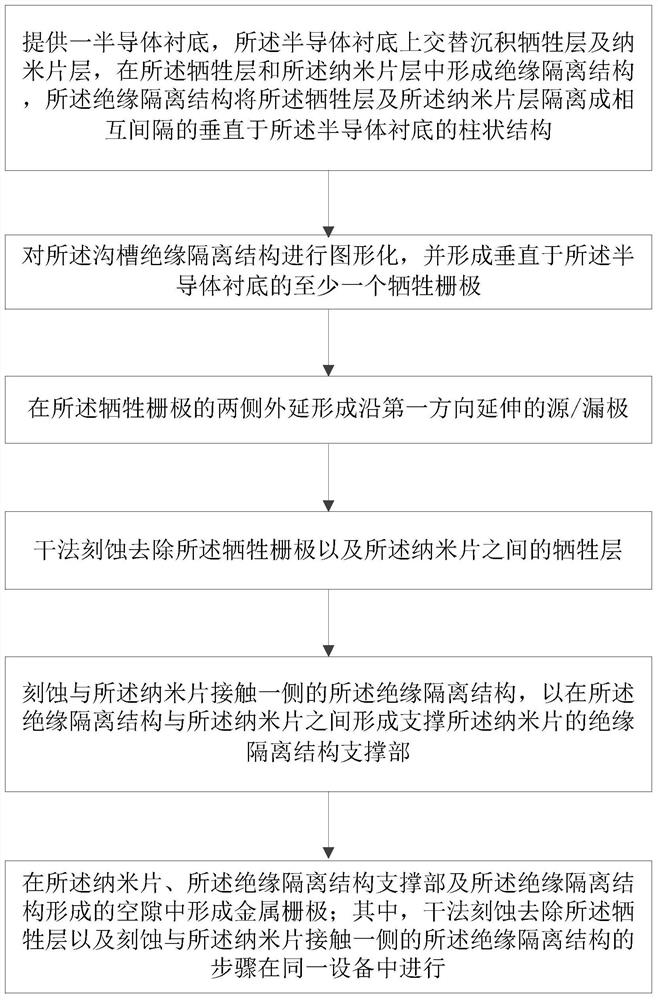

[0088] This embodiment provides a method for preparing a nanosheet field effect transistor, such as image 3 As shown, the method includes the following steps:

[0089] A semiconductor substrate is provided, on which a sacrificial layer and a nanosheet layer are alternately deposited, an insulating isolation structure is formed in the sacrificial layer and the nanosheet layer, and the insulating isolation structure separates the sacrificial layer and the nanosheet layer The nanosheets are isolated into columnar structures perpendicular to the semiconductor substrate spaced apart from each other;

[0090] patterning the insulating isolation structure, and forming at least one sacrificial gate perpendicular to the semiconductor substrate;

[0091] epitaxially forming source / drain extending along a first direction on both sides of the sacrificial gate;

[0092] dry etching to remove the sacrificial gate and the sacrificial layer between the nanosheets;

[0093] Etching the ins...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com