Three-dimensional NAND flash memory device and preparation method thereof

A flash memory, three-dimensional technology, applied in electrical components, electrical solid devices, circuits, etc., can solve problems such as difficulty in forming embedded chips, and achieve the effect of improving space utilization efficiency and reducing horizontal occupied area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

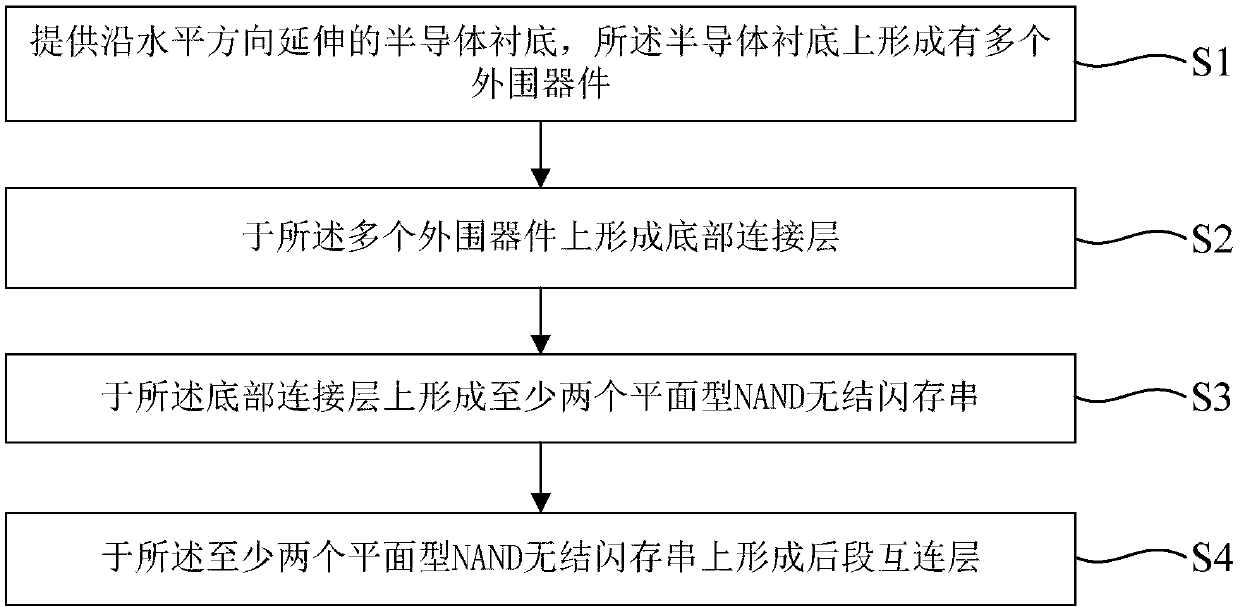

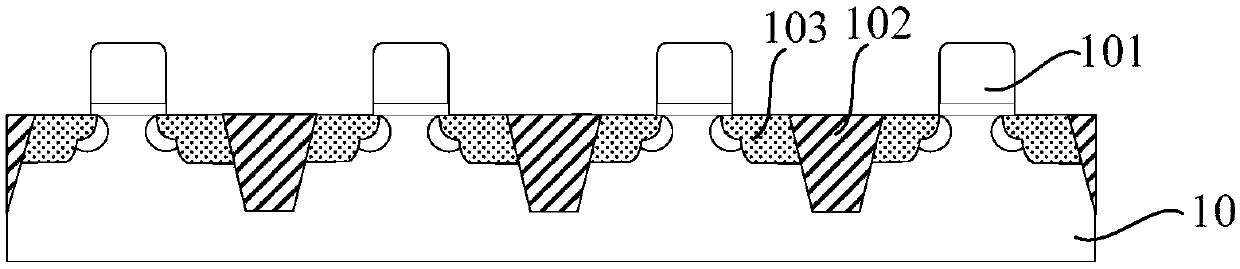

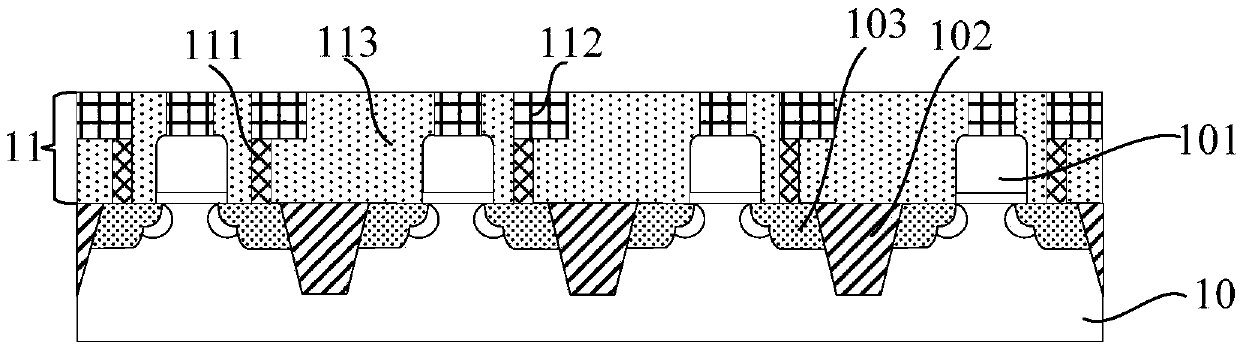

[0082] Such as figure 1 As shown, the present embodiment provides a method for preparing a three-dimensional NAND flash memory device. In this embodiment, a planar NAND junction-free flash memory string (i.e., a two-dimensional charge trap junctionless field-effect transistor flash memory) structure is combined with a peripheral device (i.e., a PUC, Peri Under Cell) are combined to build a three-dimensional NAND flash memory device. The fast read characteristics of the planar NAND junction-free flash memory string are well utilized, and it is well compatible with the logic unit, so it can be well applied in the embedded NAND flash memory device, and can also be made as a standard independent NAND flash memory products; on the other hand, PUC technology is used to stack the peripheral circuits used to drive the planar NAND junction-free flash memory strings under the planar NAND junction-free flash memory strings for storing data. The required parking lot is rebuilt from the s...

Embodiment 2

[0101] Such as Figure 14 to Figure 15 as shown, Figure 15 for Figure 14 The structure shown is a top view of the structure layer of the planar NAND junction-free flash memory string 22. The purpose is to clearly express the horizontal distribution of the planar NAND junction-free flash memory string 22. This embodiment provides a three-dimensional NAND flash memory device. The three-dimensional NAND flash memory device can be prepared by the preparation method described in Example 1, or by other methods, which are not limited here. The three-dimensional NAND flash memory device includes at least:

[0102] a semiconductor substrate 20 extending in the horizontal direction, on which a plurality of peripheral devices are formed;

[0103] a bottom connection layer 21, the bottom connection layer 21 is formed on the peripheral device;

[0104] At least two planar NAND junction-free flash memory strings 22, the at least two planar NAND junction-free flash memory strings 22 ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com