Zero-value register implementation method and device

An implementation method and register technology, applied in register devices, machine execution devices, etc., can solve the problems of logic complexity, increase implementation complexity, increase register renaming logic complexity, etc., and achieve the effect of reducing complexity and simplifying logic implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

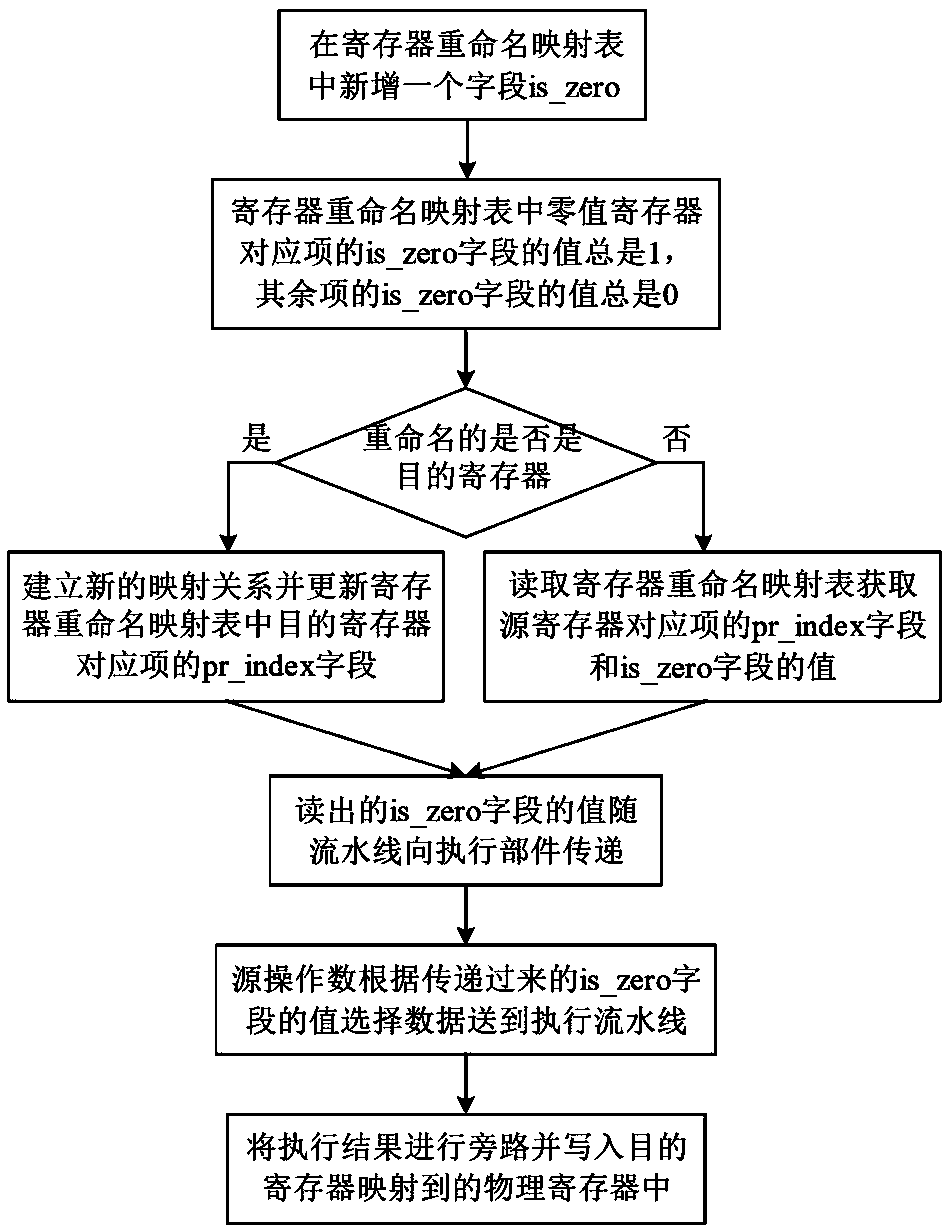

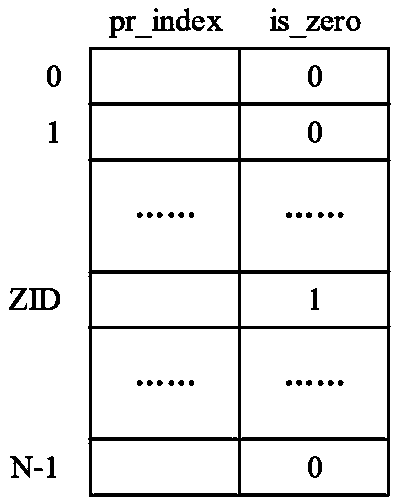

[0024] like figure 1 The implementation steps of the implementation method of the zero value register of the present embodiment shown include:

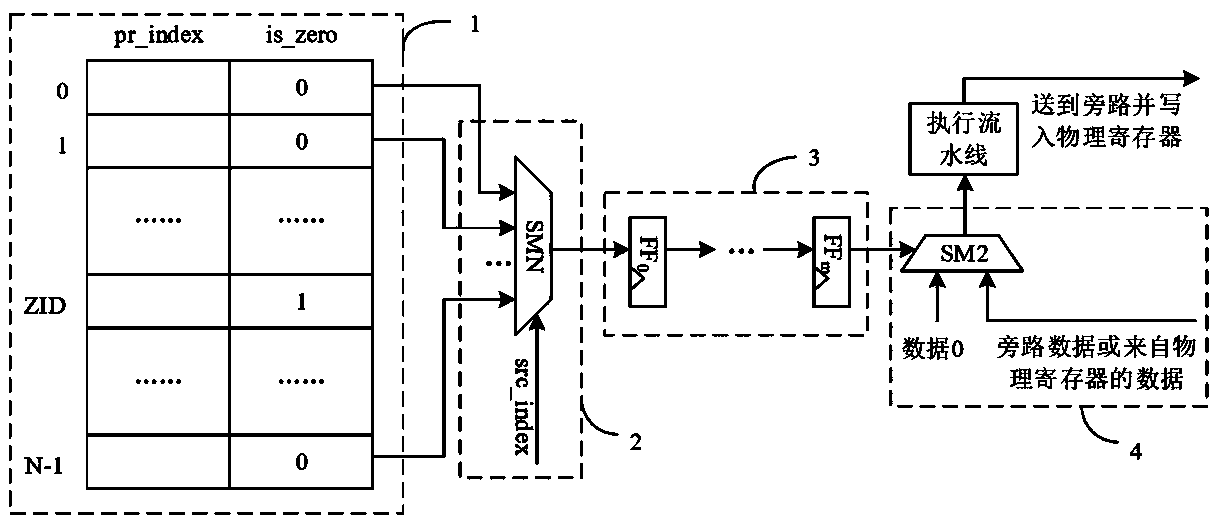

[0025] 1) In the register renaming stage of instruction execution, judge whether the renamed register is the destination register, if it is the destination register, establish a new mapping relationship from the architectural register to the physical register, and update the register in the register renaming mapping table The number field pr_index of the physical register mapped to; if it is a source register, read the number field pr_index of the physical register mapped to the register in the register renaming mapping table, indicating whether it is a zero value register. The identification field is_zero; will identify the field is_zero is passed to the execution unit along the pipeline;

[0026] 2) In the instruction launch execution stage, the source operand selects data and sends it to the execution pipeline according to the val...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com