High-frequency narrow-pulse semiconductor laser driving circuit

A driving circuit and narrow pulse technology, which is applied in the field of high-frequency narrow pulse semiconductor laser driving circuit, can solve the problems that the pulse transformer cannot meet the narrow pulse output, the rise time and fall time are too large, and the single pulse signal is susceptible to interference, etc., to achieve The maintenance and replacement of components is convenient, the accuracy is maintained, and the effect of improving anti-interference ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

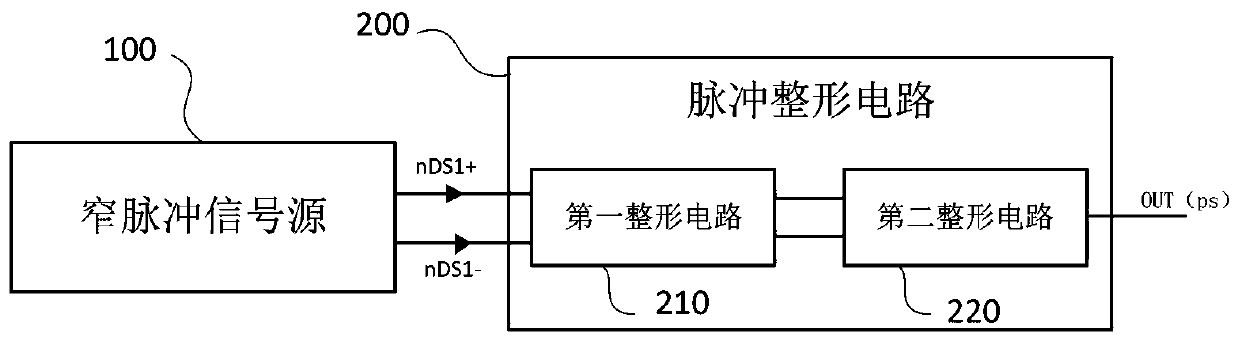

[0043] Such as figure 1 As shown, this embodiment provides a high-frequency narrow-pulse semiconductor laser drive circuit, including:

[0044] The narrow pulse signal source 100 is used to output a pair of nanosecond level differential narrow pulse signals. The nanosecond level refers to the pulse width of the pulse signal as nanosecond level; The signal output terminals are respectively connected with an output signal line, one signal line transmits the positive signal of the nanosecond differential narrow pulse signal, and one signal line transmits the negative signal of the nanosecond differential narrow pulse signal. The amplitude of the two signals is equal, the phase difference is 180 degrees, and the polarity is opposite. The traces of the two signal lines on the PCB are equal in length, equal in width, close together, and on the same level; as we all know, the inherent advantages of differential transmission signals are Strong anti-interference ability, can effective...

Embodiment 2

[0054] Such as image 3 As shown, the difference between this embodiment and Embodiment 1 is that in the semiconductor laser drive circuit of this embodiment, the first shaping circuit 210 includes a first flip-flop 211 and a first delay circuit 212; the first trigger The data input terminal D1 of the flip-flop 211 is connected to an external power supply, and the first and second clock input terminals (CLK1, CLK1-) of the first flip-flop 211 are respectively used as the first and second clocks of the first shaping circuit 210 Signal input end, the first output end Q1 of the first flip-flop 211 is connected to the input end of the first delay circuit 212 and serves as the first output end of the first shaping circuit 210, the first flip-flop The second output terminal Q1 of 211-is the second output terminal of the first shaping circuit 210, and the reset input terminal R1 of the first flip-flop 211 is connected to the output terminal of the first delay circuit 212;

[0055] T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com