Method for forming COF circuit

A circuit and substrate technology, applied in the field of COF circuit forming, can solve the problems of poor pattern, slow production speed of exposure process, poor circuit, etc., and achieve the effect of shortening processing cycle, reducing short circuit defects and reducing equipment cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

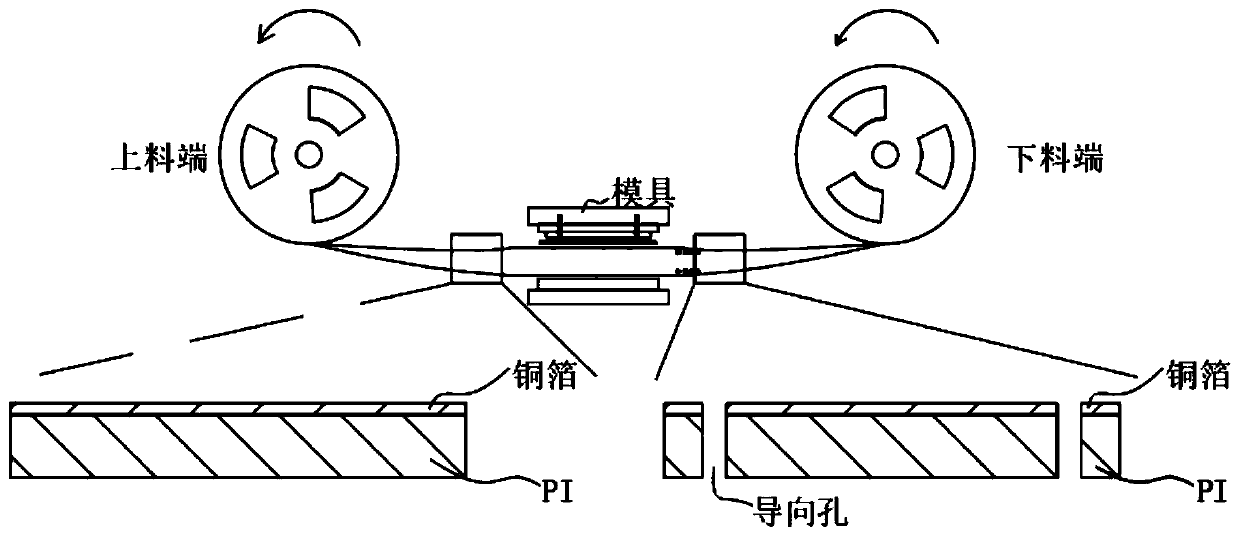

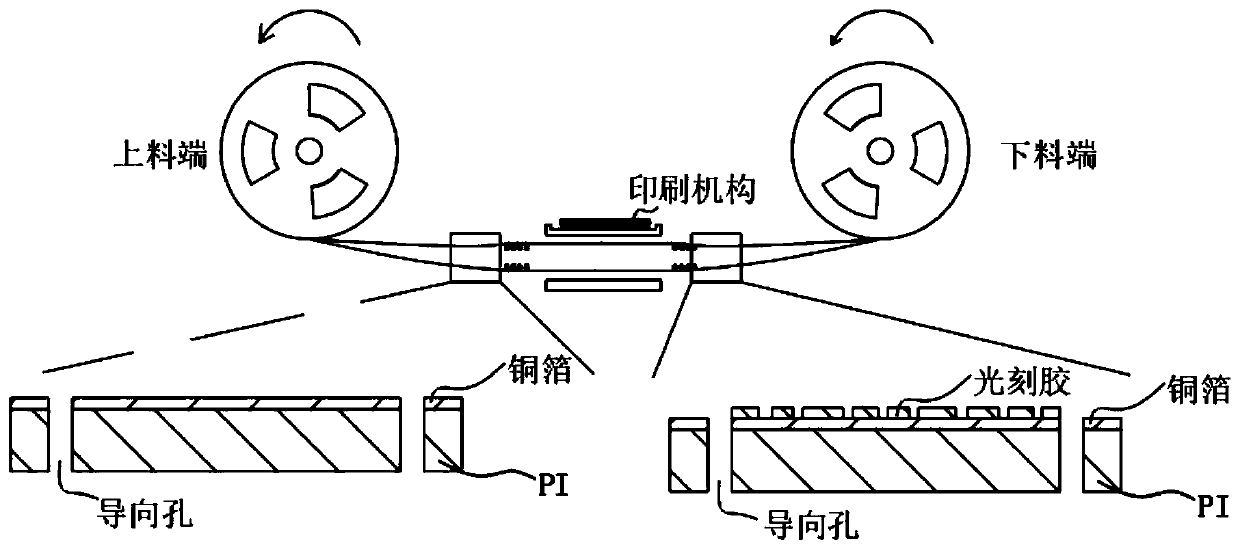

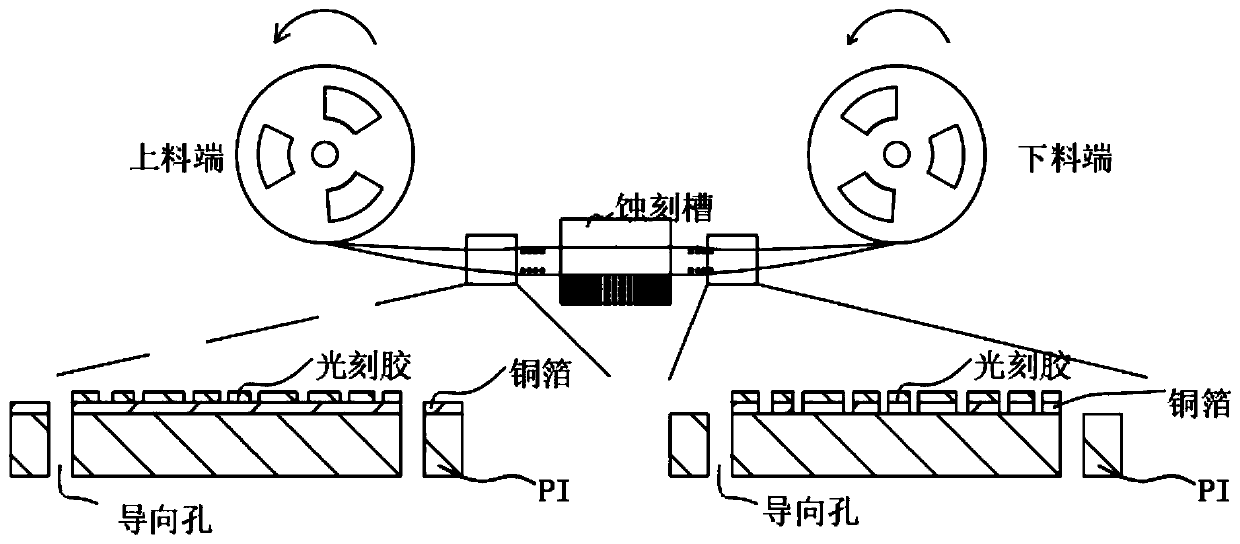

[0027] Such as Figure 1-4 As shown, the embodiment of the present invention provides a method for forming COF lines, which includes the following steps:

[0028] S1. Punching the base material and punching out the guide holes on both sides of the base material, which is convenient for the conveying operation of the later process;

[0029] S2, the punched product is printed with photoresist, and the required photoresist pattern is printed on the surface of the copper foil and cured;

[0030] S3. Perform etching on the product printed with photoresist patterns, and remove the copper that is not covered by the photoresist under the action of the etching solution;

[0031] S4. Fade the etched product, remove the photoresist pattern protected on the copper surface, and expose the circuit pattern;

[0032] S5. Follow-up processing of the product.

[0033] In the present invention, the circuit is formed by printing, and the work of the exposure and development process is omitted, thus reducin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com