Gallium oxide transistor and preparation method thereof

A gallium oxide and transistor technology, which is applied in the field of preparation of gallium oxide transistors, can solve problems such as reducing device stability, difficulty in realizing normally-off MOSFETs, and limiting performance of high-voltage field-effect transistors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

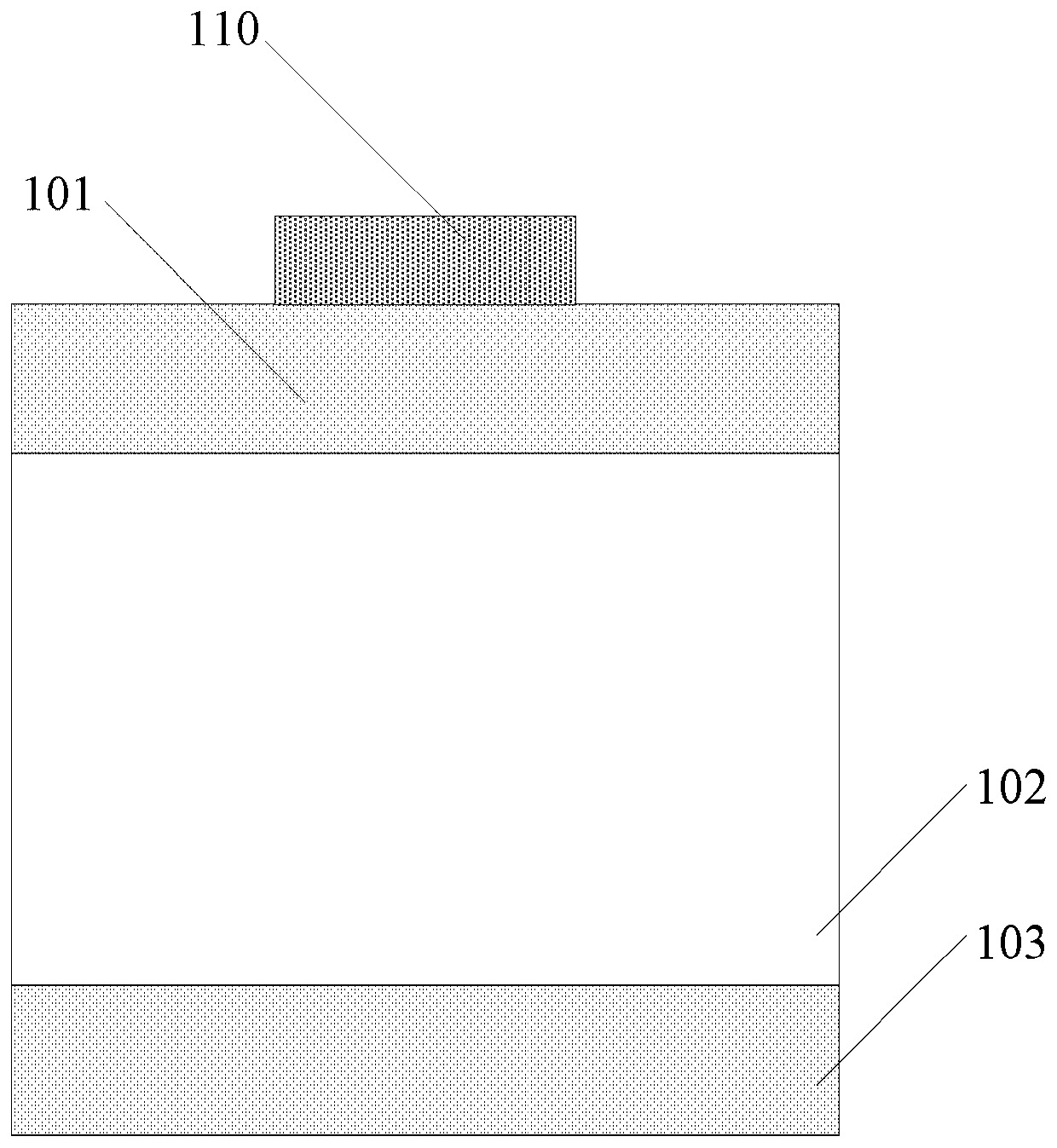

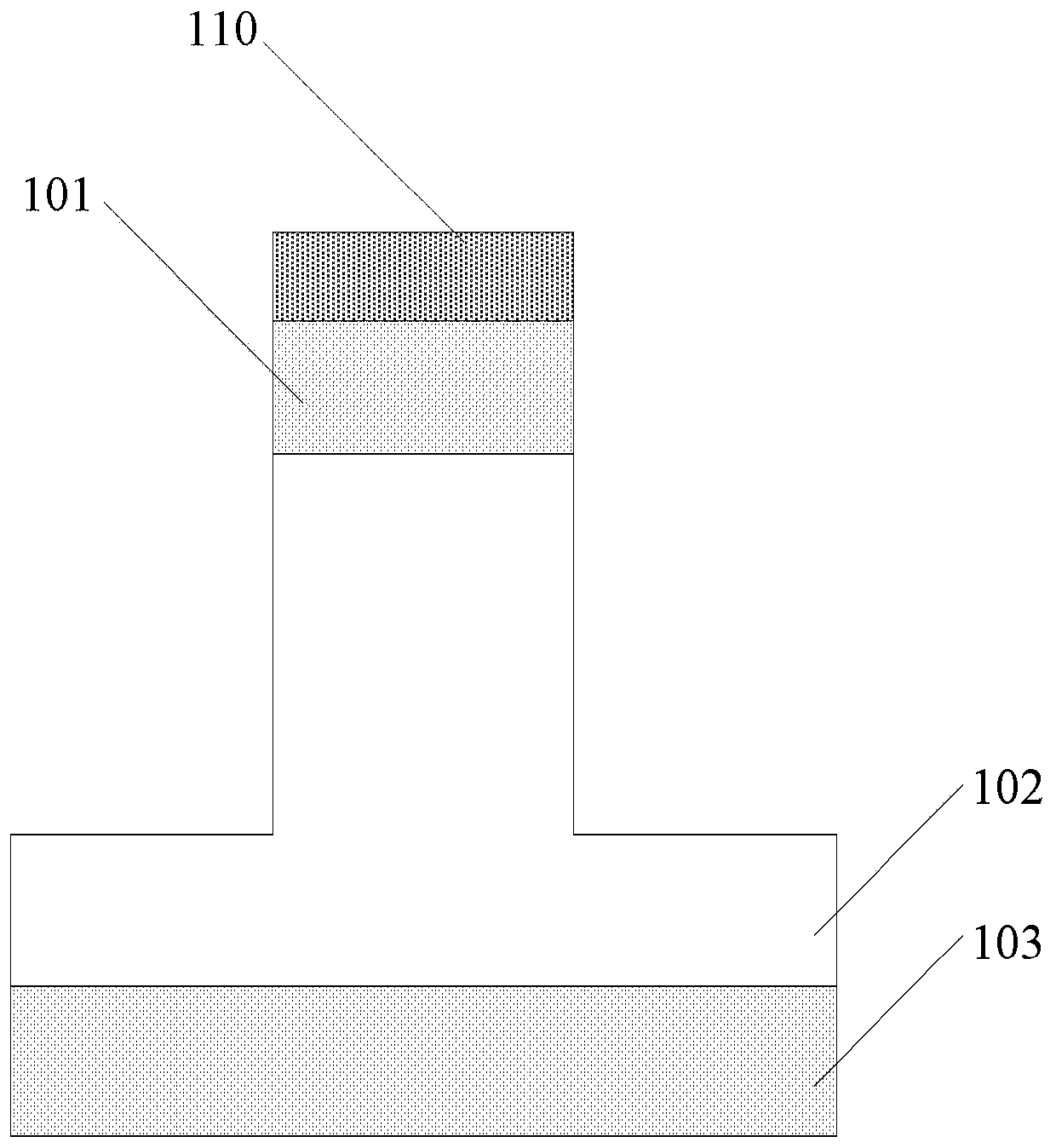

[0044] see Figure 1-8 As shown, the preparation method of the gallium oxide transistor of the specific embodiment of the present invention includes the following steps:

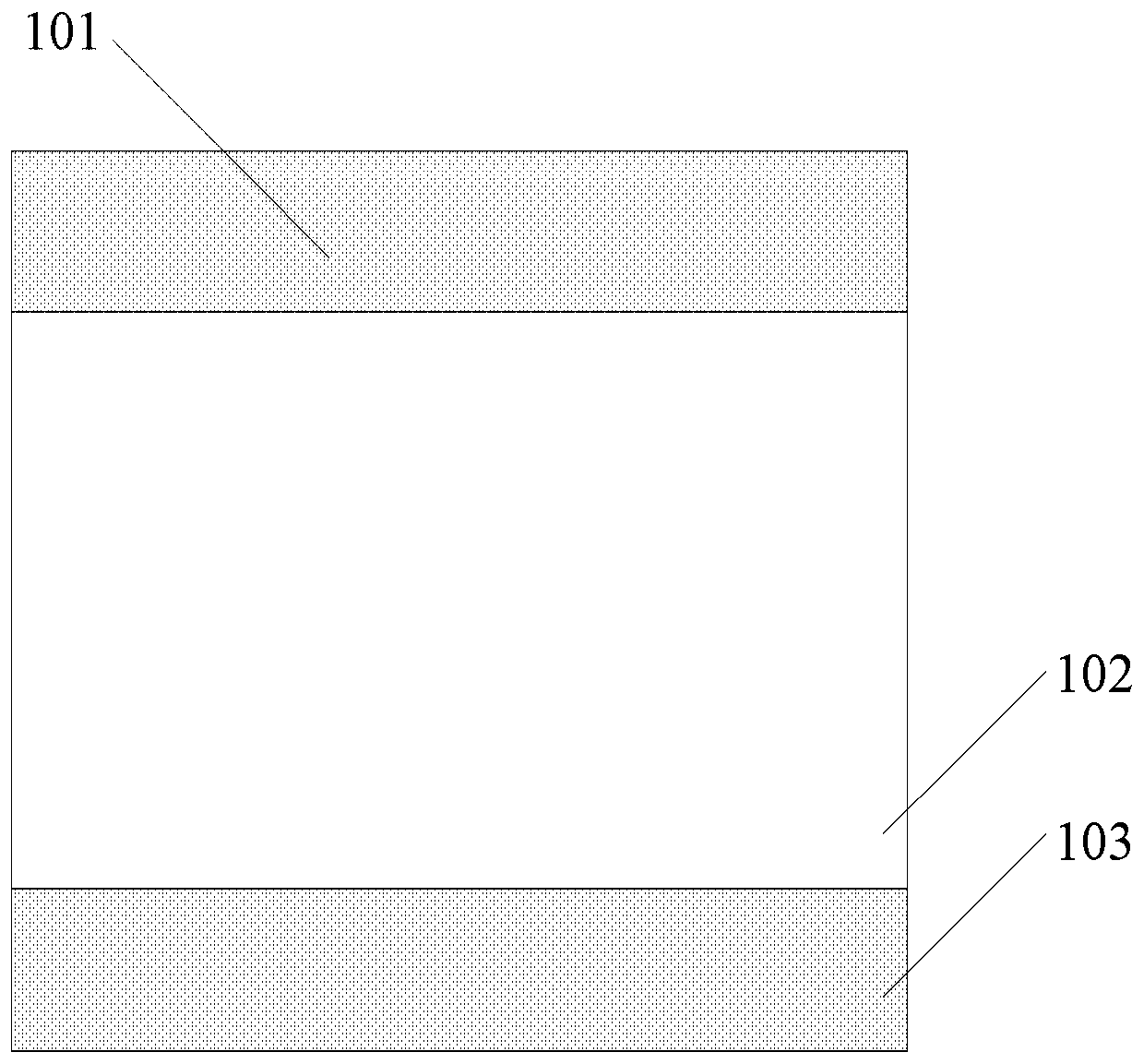

[0045] (1) Preparation of high-quality gallium oxide single crystal material, which has a three-layer structure of low resistance (high n-type doping concentration), high resistance value (low n-type doping concentration) and low resistance (high n-type doping concentration) , including a first n-type doped gallium oxide layer 103 , a second n-type doped gallium oxide layer 102 , and a third n-type doped gallium oxide layer 101 from bottom to top. The single crystal material of the first n-type doped gallium oxide layer 103 can be prepared by a guided mode method, which is a method of growing a single crystal, specifically, heating the material to a molten state through a metal iridium crucible, and then guiding the melting through a seed crystal The liquid diffuses along the gap of the mold to gradually exp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com