Retention time violation repair method, device and equipment

A hold time and violation technology, applied in the field of hold time violation repair, can solve the problems of multi-trace resources, occupation, scan chain hold time violation deterioration, etc., to achieve the effect of reducing iteration cycle and design impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

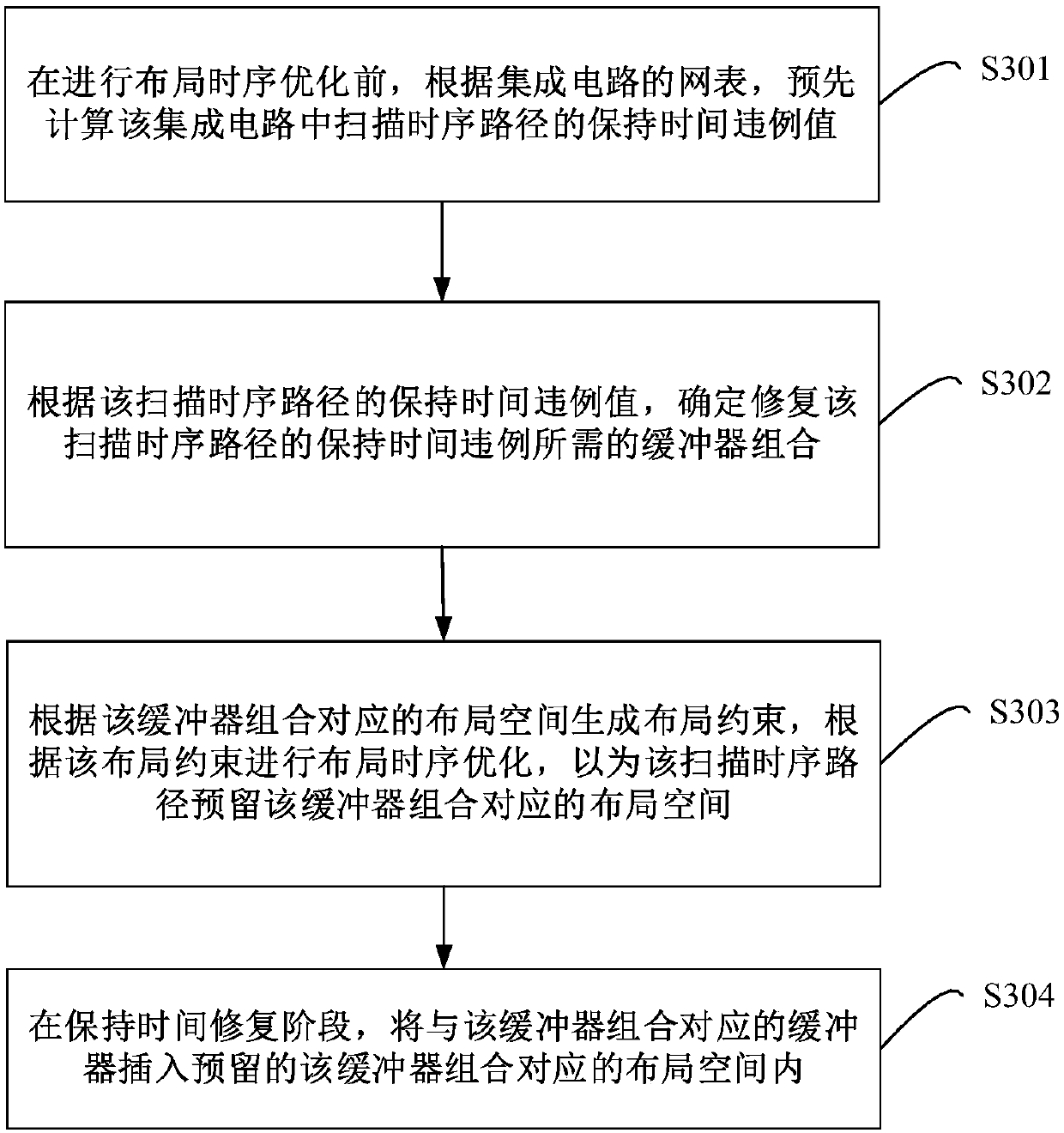

[0057] image 3 It is a flowchart of a method for repairing a hold time violation provided in Embodiment 1 of the present invention. In the embodiment of the present invention, there is not enough space to insert buffers in the hold time repair stage, or the newly inserted buffers can only be placed far away from the target area, resulting in the scan path occupying more routing resources. On the one hand, it increases The setup time of the functional path is violated. On the other hand, winding or long traces are more susceptible to coupling noise, which leads to the deterioration of the hold time violation of the scan chain. A repair method for the hold time violation is provided. Such as image 3 The specific steps of the method are as follows:

[0058] Step S301 , before performing layout timing optimization, precalculate the hold time violation value of the scan timing path in the integrated circuit according to the netlist of the integrated circuit.

[0059] Wherein, ...

Embodiment 2

[0073] Figure 4 It is a flowchart of a method for repairing a hold time violation provided in Embodiment 2 of the present invention. On the basis of the first embodiment above, in this embodiment, according to the netlist of the integrated circuit, calculating the hold time violation value of the scan timing path in the integrated circuit includes: extracting the scan timing path information and the current clock from the netlist Tree topology information; according to the scan timing path information and the topology information of the current clock tree, calculate the clock delay difference between the start timing device and the end timing device of the scan timing path; according to the start timing device information and the end timing device Information to determine the data delay of the start sequential device and the hold time of the end sequential device; according to the clock delay difference between the start sequential device and the end sequential device of the ...

Embodiment 3

[0134] Figure 5 A schematic structural diagram of a device for repairing hold time violations provided by Embodiment 3 of the present invention. The device for repairing a hold time violation provided in the embodiment of the present invention can execute the processing procedure provided in the embodiment of the method for repairing a hold time violation. Such as Figure 5 As shown, the device 50 includes: a calculation module 501 , a determination module 502 , an optimization module 503 and a repair module 504 .

[0135] Specifically, the calculation module 501 is configured to pre-calculate the hold time violation value of the scan timing path in the integrated circuit according to the netlist of the integrated circuit before performing layout timing optimization.

[0136] The determining module 502 is configured to determine a buffer combination required to fix the hold time violation of the scan timing path according to the hold time violation value of the scan timing ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com