RFSoC-based SAR imaging real-time signal processing device

A technology of real-time signal and processing device, applied in the field of communication, can solve the problems of increasing design difficulty, low real-time performance, complicated system structure, etc., and achieves the effect of increasing design difficulty, reducing design difficulty and simple circuit structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be further described below in conjunction with the accompanying drawings.

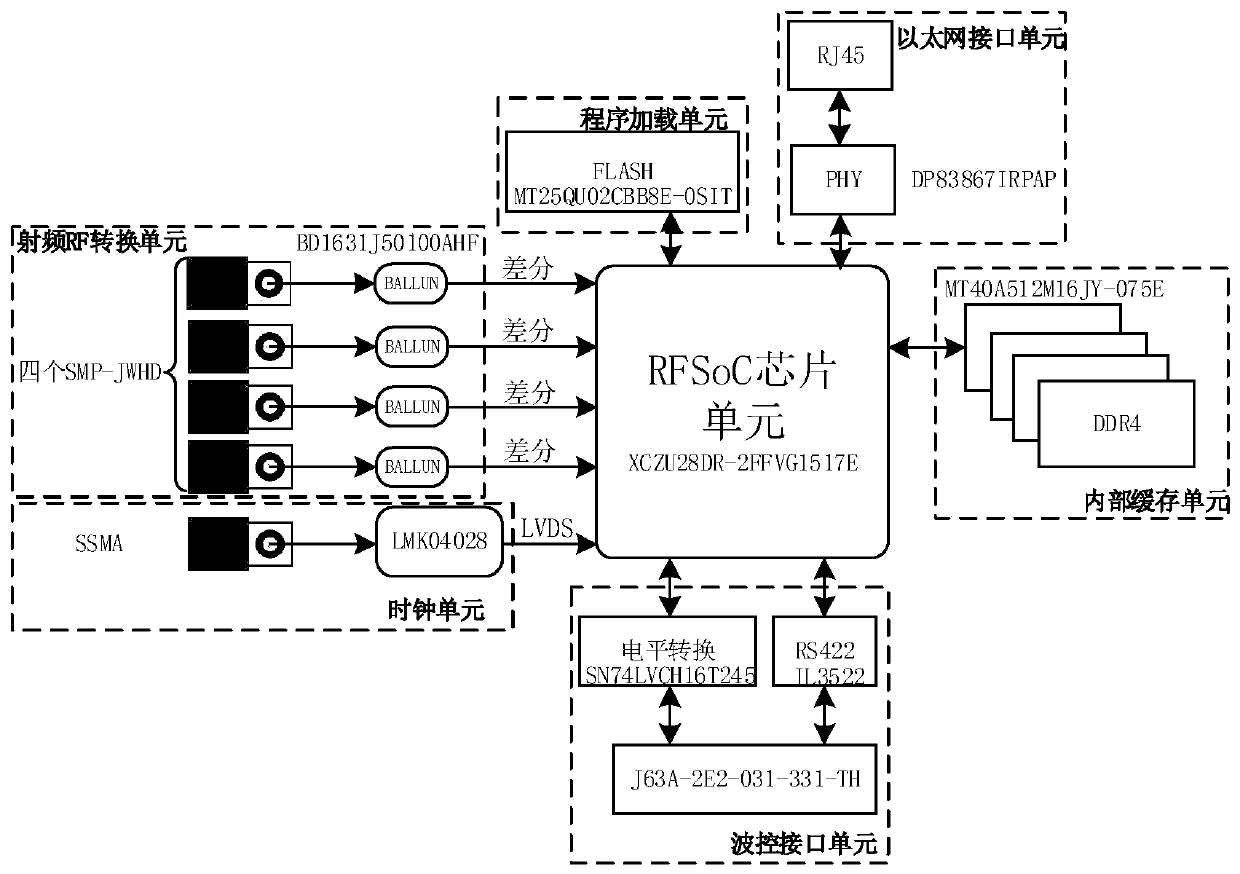

[0018] Reference attached figure 1 , to further describe the overall circuit of the present invention,

[0019] The overall circuit of the present invention includes a radio frequency RF conversion unit, a clock unit, a program loading unit, an Ethernet interface unit, an internal buffer unit, a wave control interface unit, and a radio frequency system on chip RFSoC chip unit.

[0020] In an embodiment of the present invention, the radio frequency RF conversion unit is connected to the radio frequency system-on-chip RFSoC chip unit through a differential interface, and the output interface of the radio frequency RF conversion unit has four differential interfaces, and the RFSoC chip unit of the radio frequency system-on-chip The differential interface is the analog-to-digital conversion resource sampling interface of the chip, and the output interface of the RF conver...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com