3d NAND flash memory and its preparation method

A flash memory and suppression layer technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of dielectric layer breakdown between adjacent gate layers, gate layer threshold voltage drift, and storage layer charge loss, etc. The effect of reducing threshold voltage drift, reducing leakage, and ensuring stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

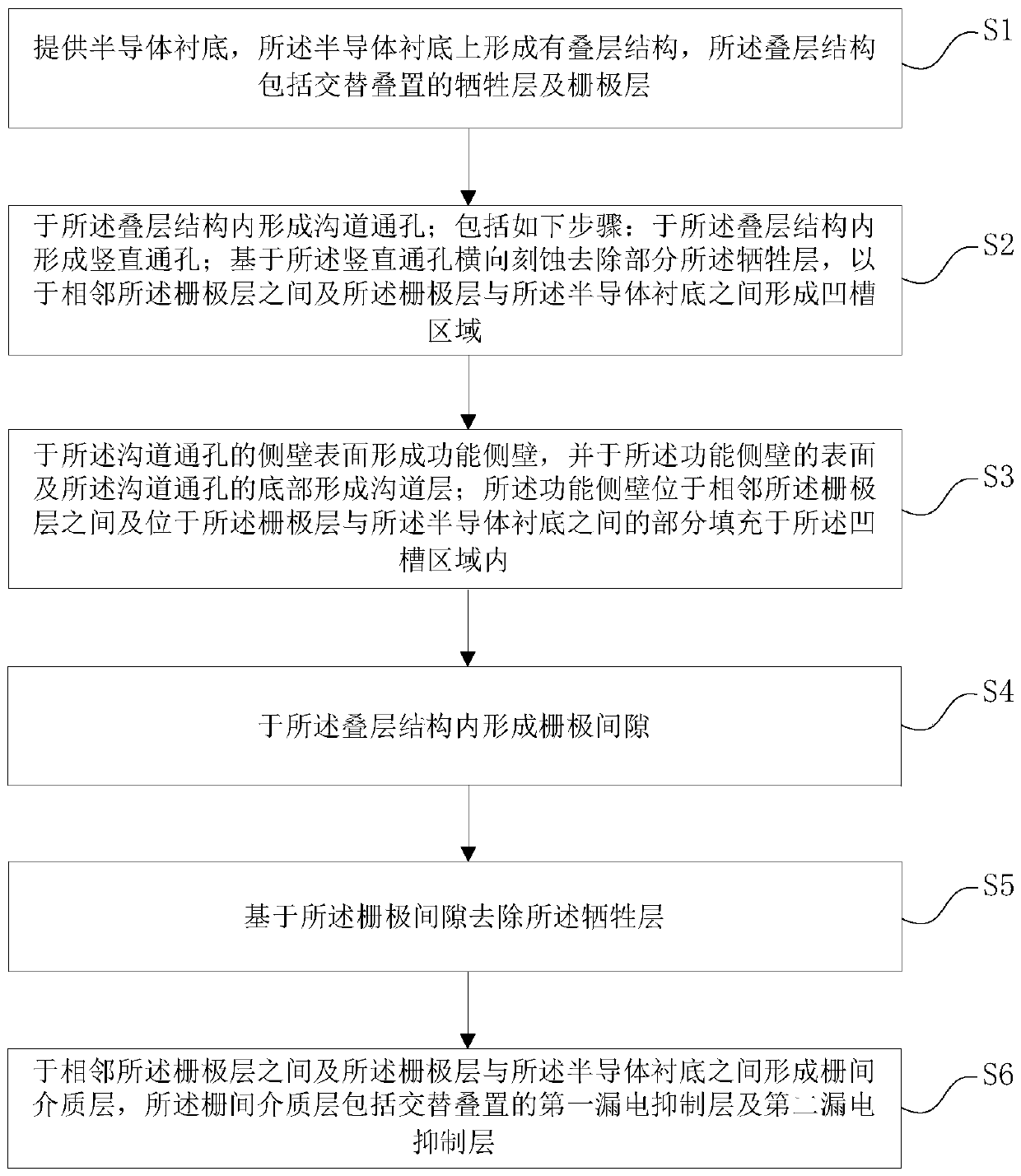

[0098] see figure 1 , the present embodiment also provides a method for preparing a 3D NAND flash memory, the method for preparing the 3D NAND flash memory includes the following steps:

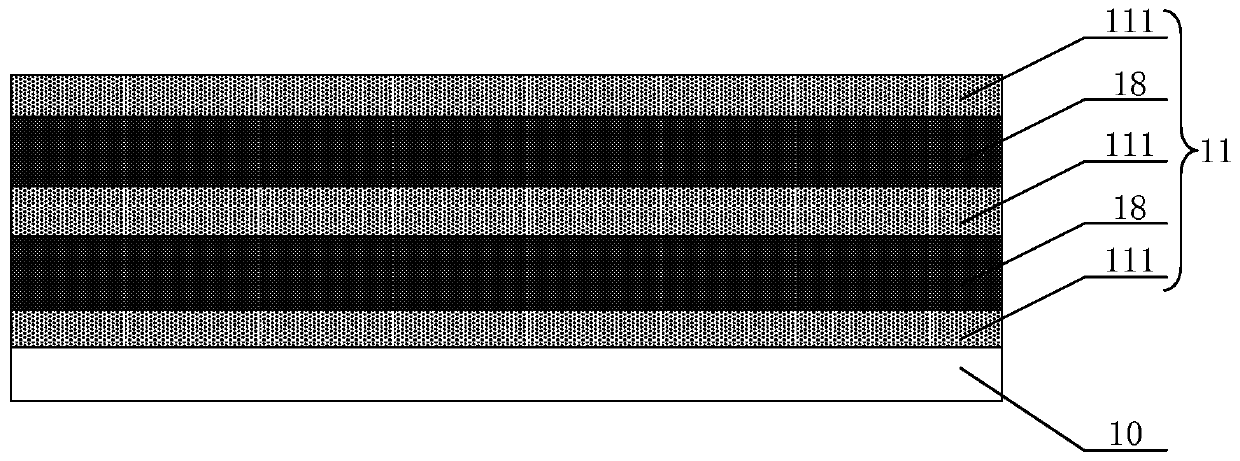

[0099] 1) providing a semiconductor substrate, on which a stacked structure is formed, and the stacked structure includes alternately stacked sacrificial layers and gate layers;

[0100] 2) Forming a channel via hole in the stacked structure; including the following steps: forming a vertical via hole in the stacked structure; laterally etching and removing part of the sacrificial layer based on the vertical via hole, to forming a groove region between adjacent gate layers and between the gate layer and the semiconductor substrate;

[0101] 3) forming a functional sidewall on the surface of the sidewall of the channel through hole, and forming a channel layer on the surface of the functional sidewall and the bottom of the channel through hole; The portion between the gate layer and between t...

Embodiment 2

[0174] read on Figure 23 and Figure 25 , this embodiment also provides a 3D NAND flash memory, the 3D NAND flash memory includes: a semiconductor substrate 10; a stacked structure 31, the stacked structure 31 is located on the semiconductor substrate 10, the stacked structure 31 includes alternately stacked inter-gate dielectric layers 17 and gate layers 18; the inter-gate dielectric layer 17 includes air gaps 173 and alternately stacked first leakage suppression layers 171 and second leakage suppression layers 172, the air The gap 173 is located in the structure in which the first leakage suppression layer 171 and the second leakage suppression layer 172 are alternately stacked; the channel via hole 12, and the channel via hole 12 is located in the stacked structure 31; The channel via hole 12 includes several groove regions 122, and the groove region 122 is located between adjacent gate layers 18 and between the gate layer 18 and the semiconductor substrate 10; the functi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com