A kind of manufacturing method of semiconductor device and semiconductor device

A manufacturing method and semiconductor technology, applied in the manufacture of semiconductor devices, in the field of semiconductor devices, can solve problems such as high surface peak electric field, increased cost, and poor breakdown stability, achieve high pinch-off voltage, reduce process cost, and high The effect of stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

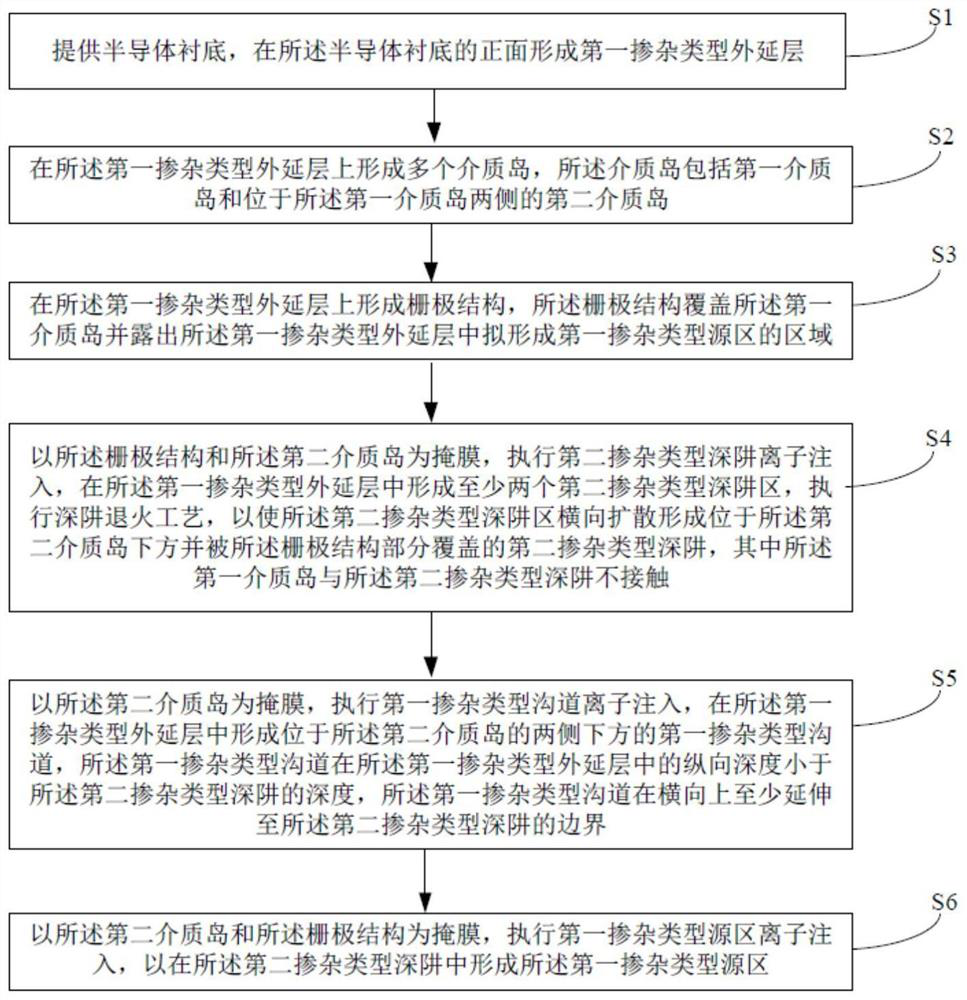

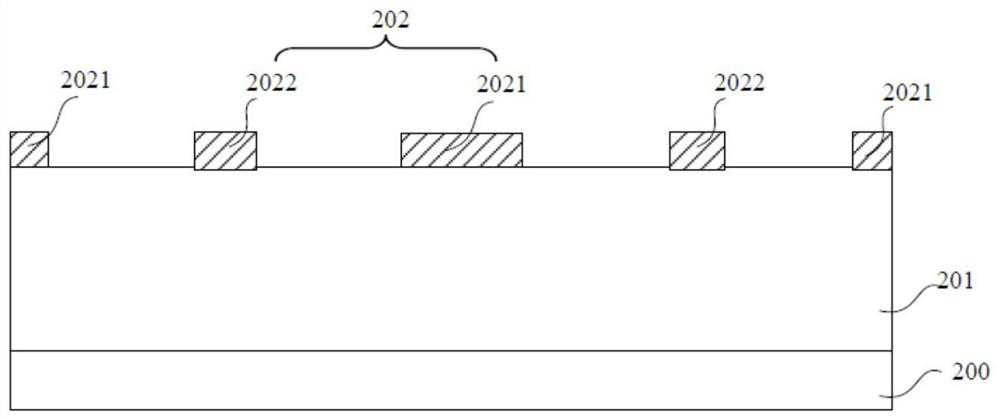

[0040] see below figure 1 and Figures 2A-2G A method for manufacturing a semiconductor device proposed by the present invention is exemplified, wherein, figure 1 It is a flowchart of a method for manufacturing a semiconductor device according to an embodiment of the present invention; Figures 2A-2G based on figure 1A schematic structural diagram of a semiconductor device formed in a method for manufacturing a semiconductor device is shown.

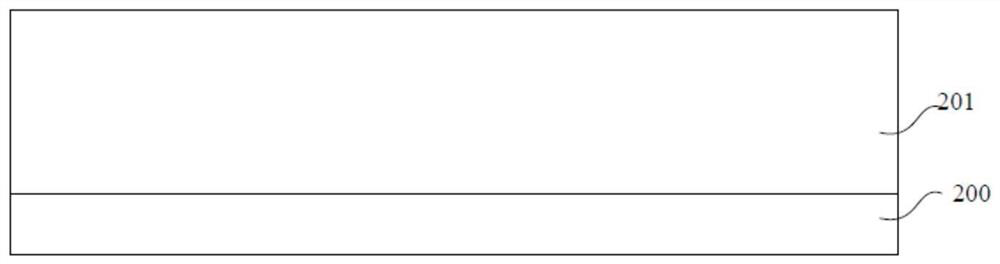

[0041] First, see figure 1 , performing step S1: providing a semiconductor substrate, and forming an epitaxial layer of the first doping type on the front surface of the semiconductor substrate.

[0042] Such as Figure 2A As shown, a semiconductor substrate 200 is provided, specifically, it may be at least one of the materials mentioned below: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP, InGaAs or other III / V compound semiconductors , including multilayer structures composed of these semiconductors, or silicon-on-insulator (SOI), si...

Embodiment 2

[0082] The present invention also provides a semiconductor device, which includes the semiconductor device obtained by the manufacturing method in Embodiment 1. The semiconductor device includes:

[0083] semiconductor substrate;

[0084] a first doping type epitaxial layer located on the front side of the semiconductor substrate;

[0085] a dielectric island located on the first doped type epitaxial layer;

[0086] a gate structure located on the first doped type epitaxial layer, the gate structure covering the dielectric island and part of the first doped type epitaxial layer;

[0087] The second doping type deep well is located on both sides of the dielectric island and in the first doping type epitaxial layer, and a part of the second doping type deep well is located below the gate material layer, And the deep well of the second doping type is not in contact with the dielectric island;

[0088] The source region of the first doping type is located on both sides of the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| length | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com