Chip input pin ESD protection circuit architecture with ultralow leakage current

An ESD protection, ultra-low leakage technology, applied in the electronic field, can solve the problems of reducing output impedance, ESD damage failure, increasing the secondary processing cost of sensors, etc., and achieve the effect of ultra-high input impedance performance and low-cost application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

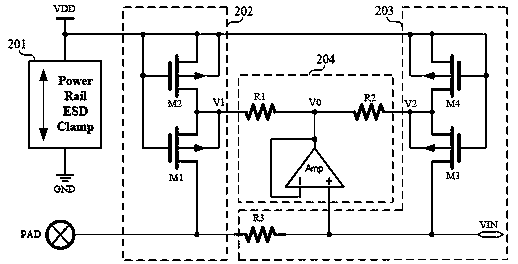

[0015] Such as figure 1 As shown, the patent of the present invention is an input pin ESD protection circuit architecture that can be integrated in a SOC chip to achieve ultra-high input impedance, which includes a power ground ESD clamp 201, a first-stage ESD protection module 202, a second stage ESD protection module 203 and leakage current transfer absorbing buffer 204 .

[0016] The power ground ESD clamper 201 realizes the real-time monitoring of the electrostatic pulse between the chip power supply and the ground, which can timely release the positive and negative electrostatic pulses between the power supply and the ground, and clamp the voltage between the power supply ground to the internal devices of the chip Within the acceptable safe voltage range, when there is no electrostatic pulse between the power supply and the ground, the power ground ESD clamp 201 does not affect the power supply of the chip power ground.

[0017] The first-level ESD protection module 202 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com