An Extended Method of Parallel Bus Serial Interconnection with Error Correction and Automatic Response Mechanism

A technology of automatic response and extension method, which is applied in the fields of climate sustainability, instrumentation, electrical digital data processing, etc., and can solve the problem of high signal integrity and bus drive requirements, complex board-level wiring and backplane wiring, FPGA pin Large quantity and other problems, to achieve the effect of easy guarantee of signal integrity, improvement of reliability and reduction of complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

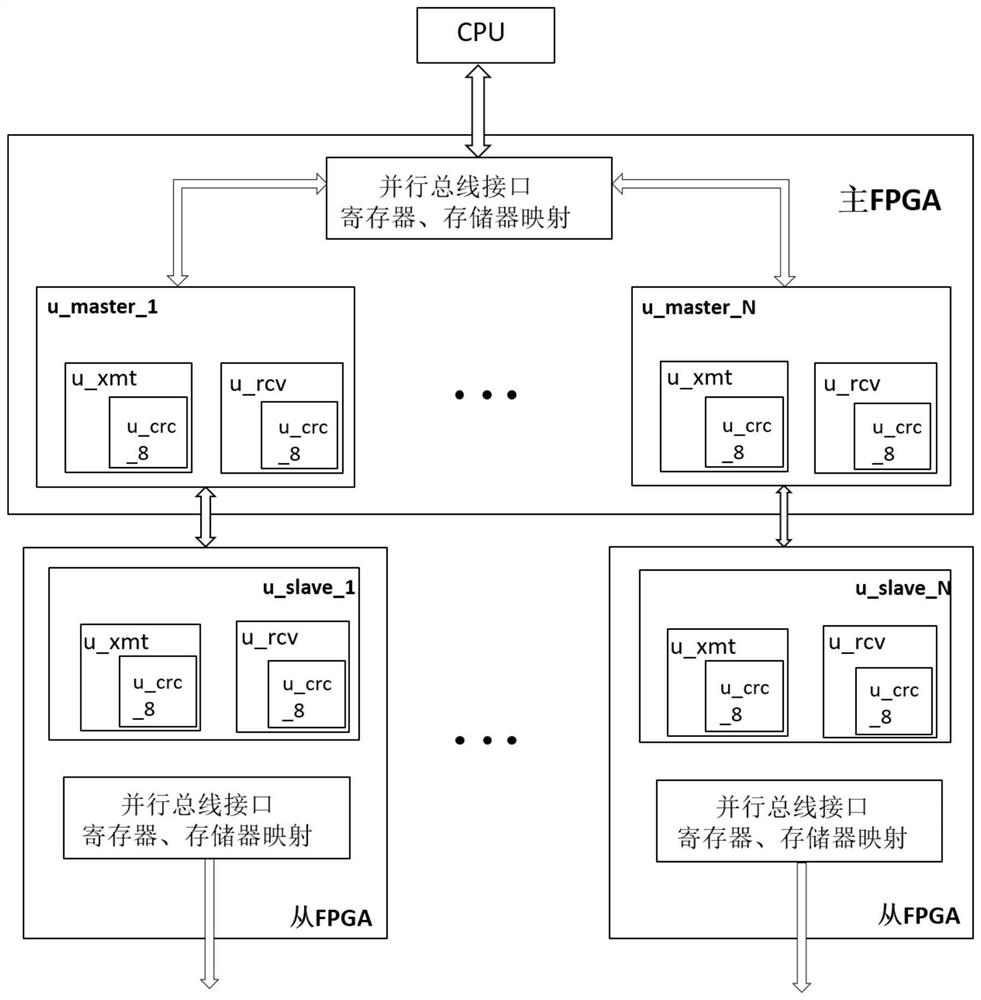

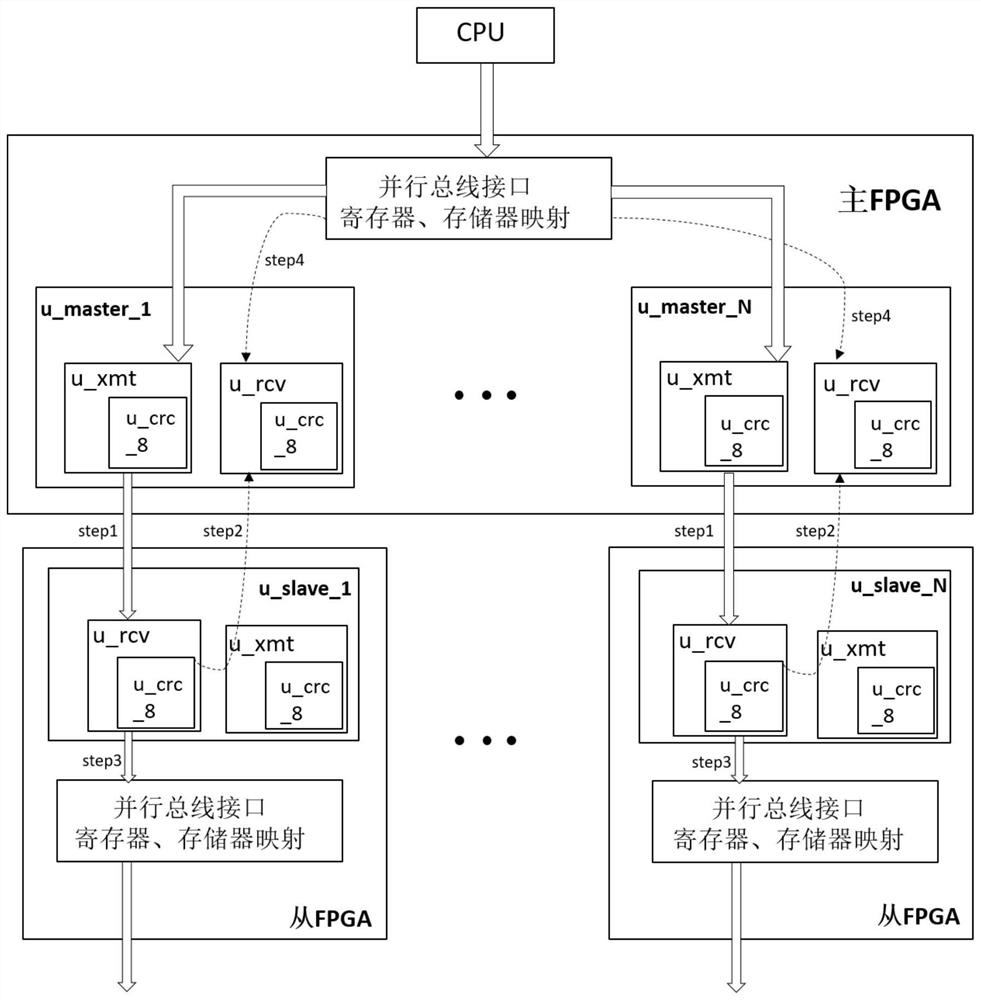

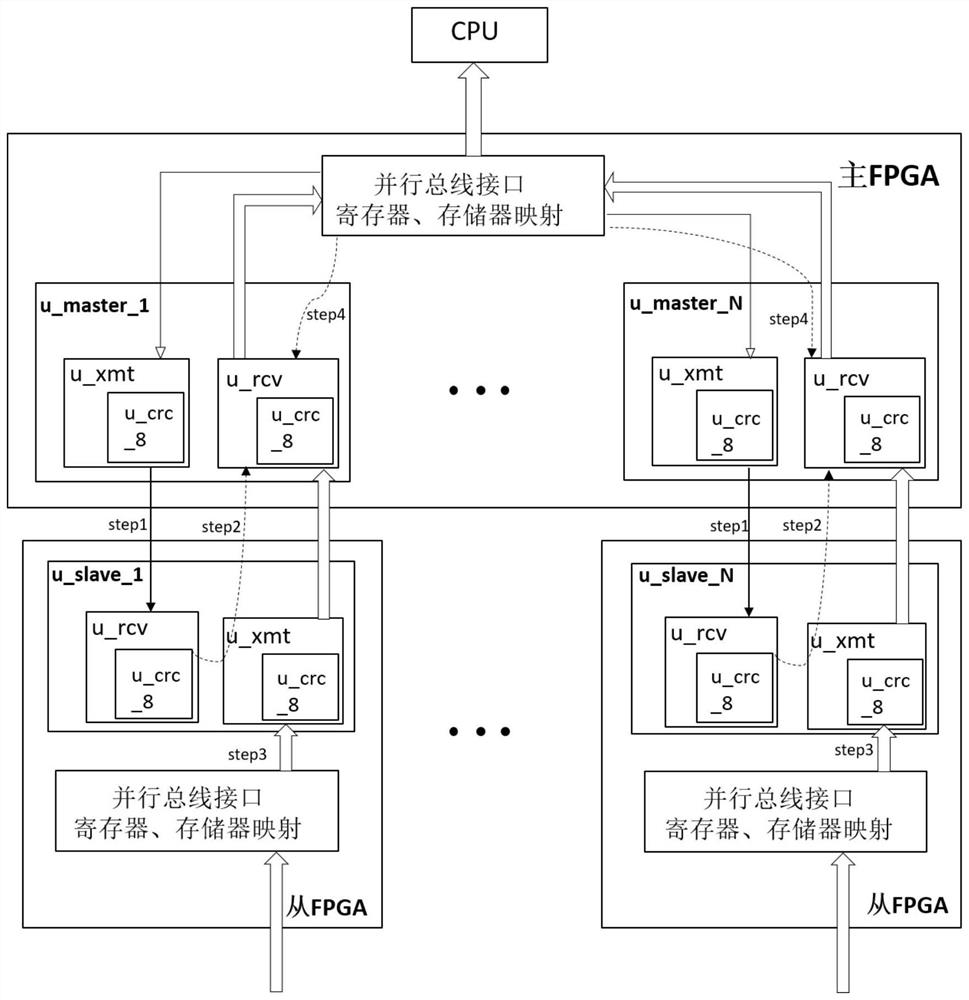

[0010] The present invention expands the parallel bus in the way of serial communication, so that the CPU can manage a large number of FPGAs in the way of indirect storage access and can save the memory mapping space; the common serial communication mode (such as Asynchronous serial mode) to reduce the complexity of board-level wiring and backplane wiring; the communication between the master and slave serial bus interface circuits has its own verification and response mechanism, which can detect operation errors in time. This communication method is flexible, reliable, simple, interactive and easy to expand

[0011] The present invention will be further described below in conjunction with the accompanying drawings.

[0012] combine figure 1 , The parallel bus serial interconnection expansion method with error correction and automatic response mechanism of the present invention includes a CPU, a master FPGA and a slave FPGA, and the system connects the CPU and multiple slave ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com