A FPGA-based mapping-oriented network-on-chip verification method and system

A network-on-chip and verification method technology, applied in the field of mapping-oriented network-on-chip verification, can solve the problems of lack of mapping power consumption, restore the working environment of multi-core systems, and do not conform to hardware conditions, and achieve the effect of rapid simulation evaluation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In the following, the present invention will be further described in detail in conjunction with the accompanying drawings and embodiments, so as to make the purpose, technical solutions and advantages of the present invention more clear. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

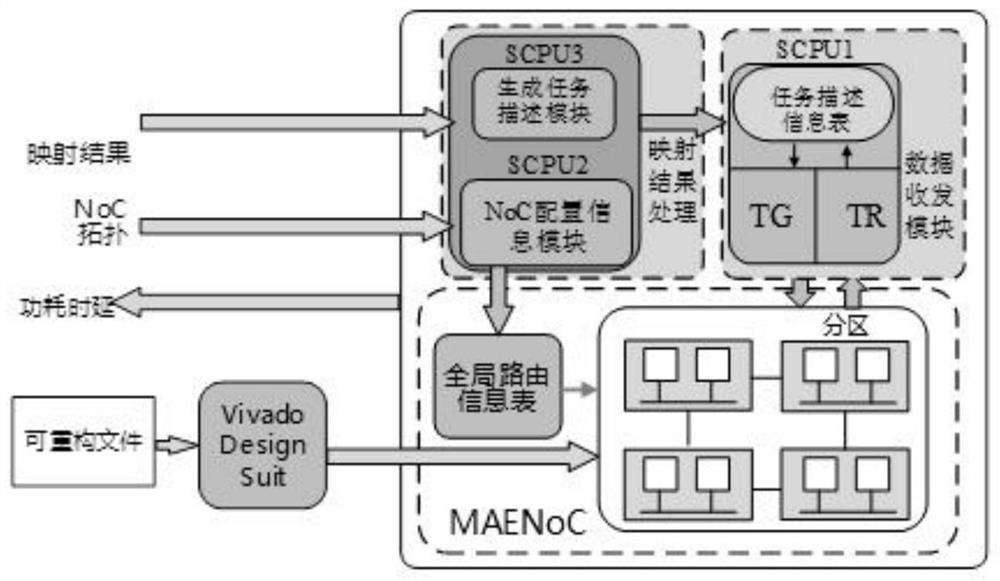

[0030] figure 1 A map-oriented network-on-chip verification method according to an exemplary embodiment of the present invention is shown. The method of this embodiment mainly includes:

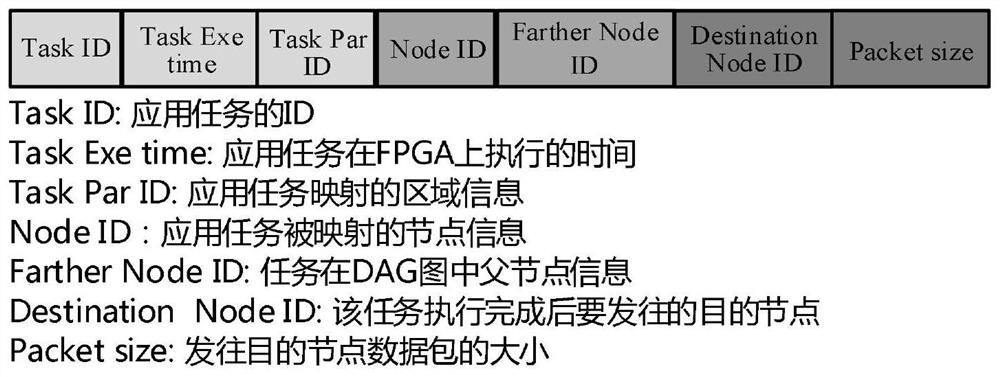

[0031] S101: Obtain the application input by the user and the topology structure of the network on chip set by the user, select a mapping algorithm, and use the mapping algorithm to map the nodes of the application to the nodes corresponding to the network on chip set by the user, and obtain mapping the result and outputting the mapping result;

[0032] S102: Set the routing table of each node of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com