Bottom trench Schottky contact sic MOSFET device

A technology of Schottky contact and groove bottom, which is applied in the field of electronic science, can solve the problems of large leakage current in the blocking state, achieve good short-circuit capability, avoid bipolar degradation problems, low reverse turn-on voltage and conduction loss Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

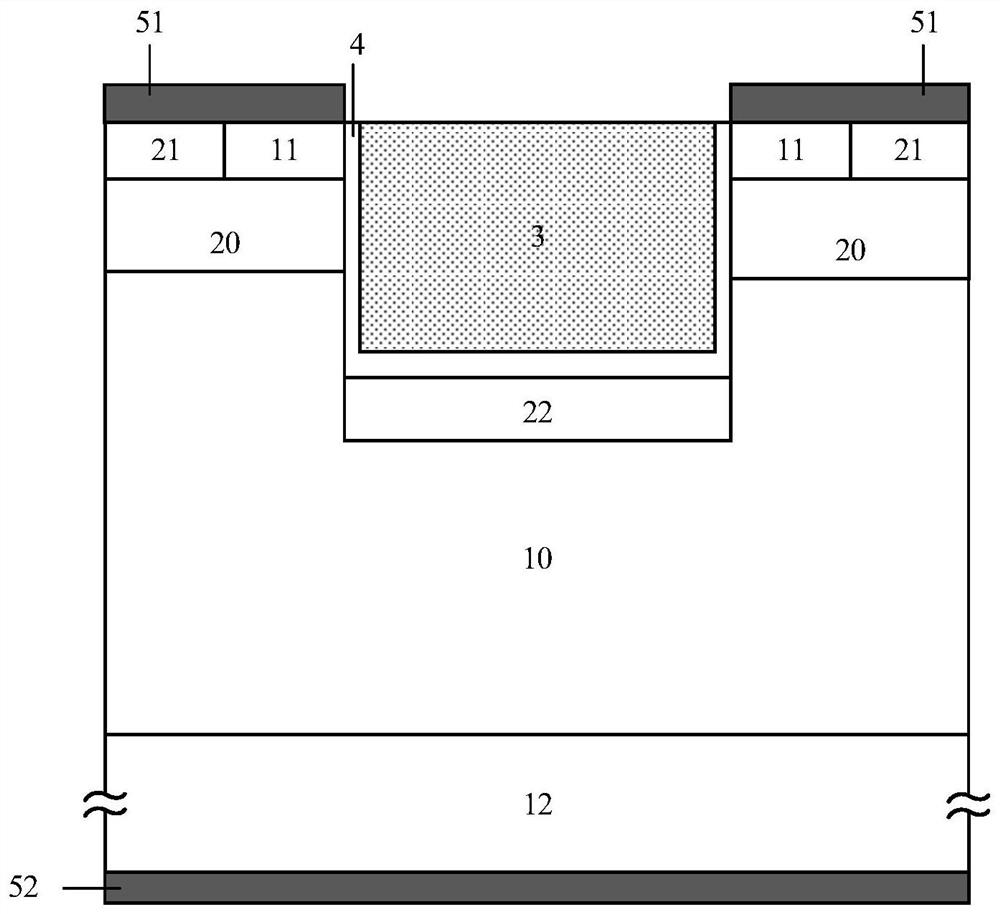

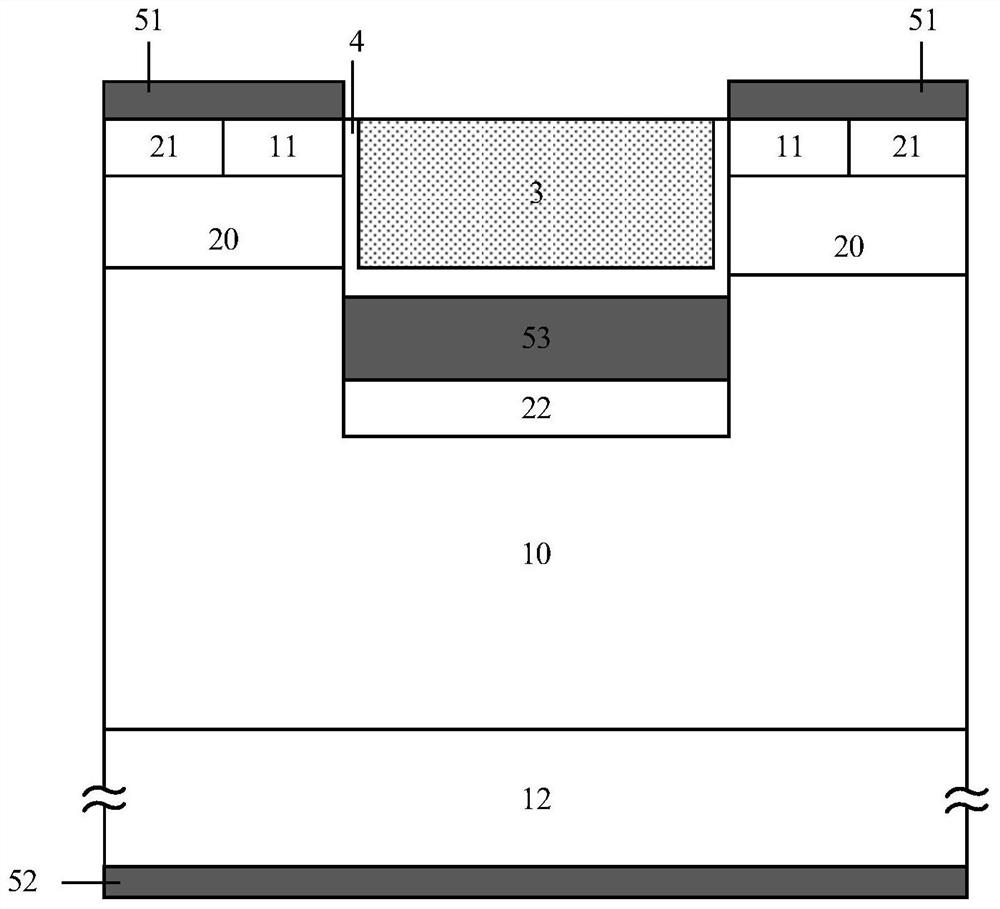

[0034] Such as figure 2 As shown, the groove bottom Schottky contact SiC MOSFET device of this embodiment includes: an N-type substrate 12, an N-type epitaxial layer 10 located above the N-type substrate 12, and a P-body located above the N-type epitaxial layer 10 Region 20, P+ contact region 21 and N+ contact region 11 located above P-body region 20, oxide layer 4 and gate 3 located between P-body region 20, Schottky contact electrode located below gate 3 53, and the oxide layer 4 is filled between the Schottky contact electrode 53 and the gate 3, the Schottky contact electrode 53 forms a Schottky contact with the N-type epitaxial layer 10, and the P- The shield region 22, the source 51 located above the P+ contact region 21 and the N+ contact region 11, and the source 51 forms ohmic contacts with the P+ contact region 21 and the N+ contact region 11 at the same time, and the drain located below the N-type substrate 12 52 , and the drain 52 forms an ohmic contact with the N...

Embodiment 2

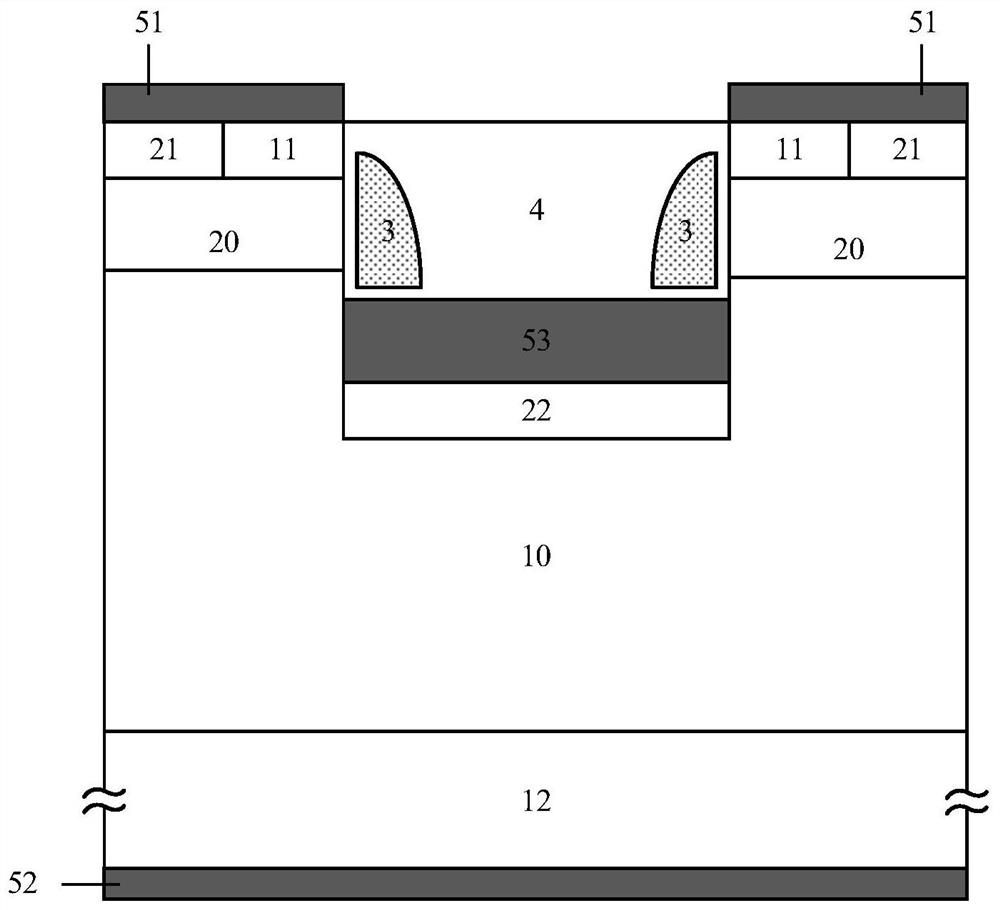

[0041] Such as image 3 As shown, the difference between the device structure of this embodiment and Embodiment 1 is that the gate 3 is split into two side gates, and the middle of the side gates is filled with an oxide layer 4 .

Embodiment 3

[0043] Such as Figure 4 As shown, the main difference between this embodiment and Embodiment 1 is that the gate 3 is split into two side gates, and the middle of the side gates is filled with metal so that the source electrode 51 and the Schottky contact electrode 53 are connected to form the same area, which is metal electrode 54 . An oxide layer 4 is filled between the metal electrode 54 and the gate 3 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com