A SiC MOSFET device incorporating a Schottky diode

A Schottky diode and Schottky contact technology, applied in diodes, semiconductor devices, electrical components, etc., can solve problems such as large leakage current in blocking state, suppress excessive electric field, avoid bipolar degradation, and improve overall Effects of Electrical Characteristics and Reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

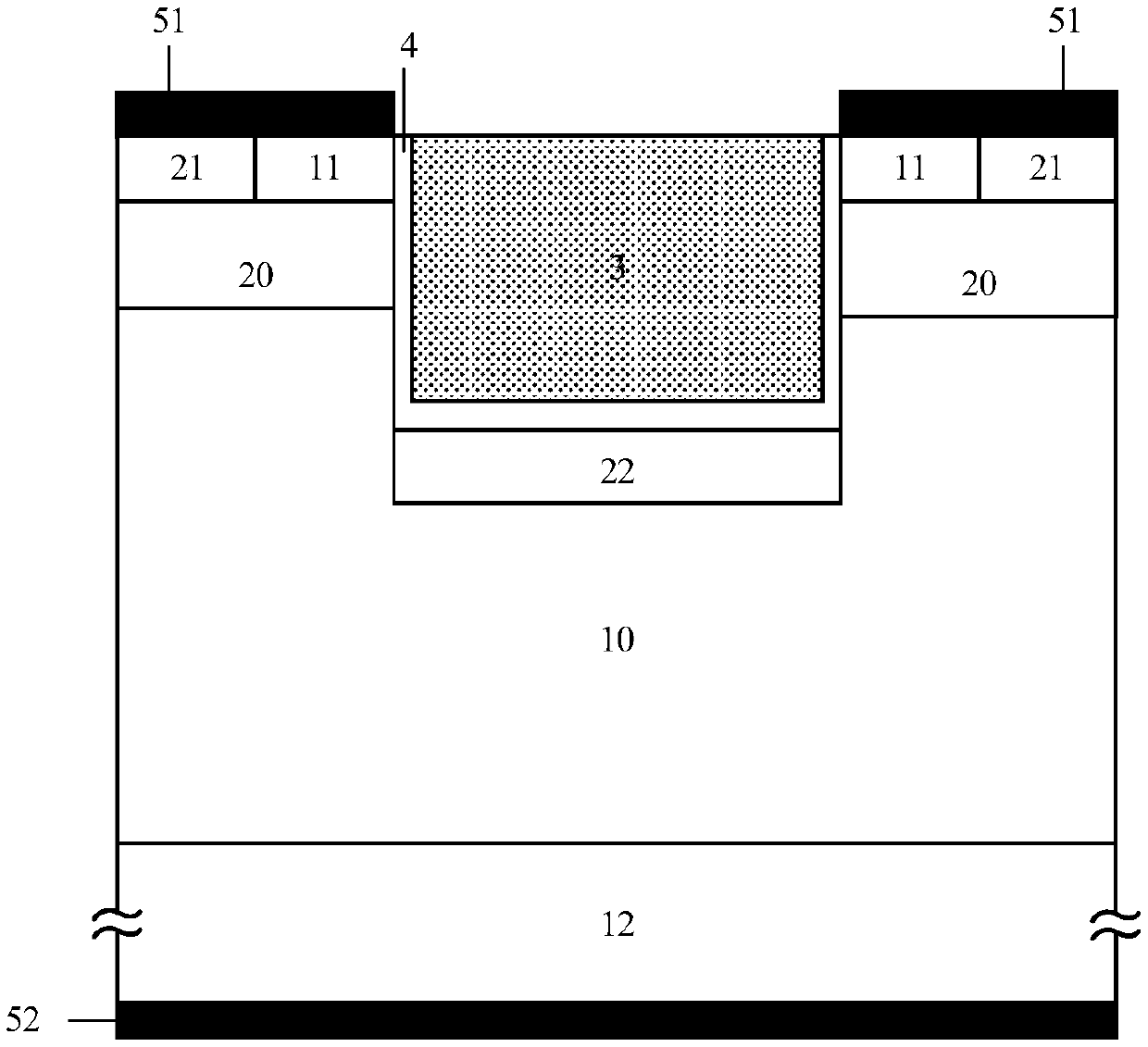

[0028] Such as figure 2 As shown, the SiC MOSFET device integrated Schottky diode in this embodiment includes: an N-type substrate 12, an N-type epitaxial layer 10 located above the N-type substrate 12, and a P-body located above the N-type epitaxial layer 10 Region 20, P+ contact region 21 and N+ contact region 11 located above P-body region 20, oxide layer 4 and side gate 3 located between P-body region 20, P-shield region 22 located below side gate 3, The metal electrode 51 located above the device, the drain 52 located below the device and forming ohmic contact with the N-type substrate 12; the metal electrode 51 is in ohmic contact with the P+ contact region 21 and the N+ contact region 11 to form the device source, and at the same time The groove bottom forms a Schottky contact with the N-type epitaxial layer 10, and the P-shield region 22 at the groove bottom is a continuous area.

[0029] This example works as follows:

[0030] When the device is in normal use, the ...

Embodiment 2

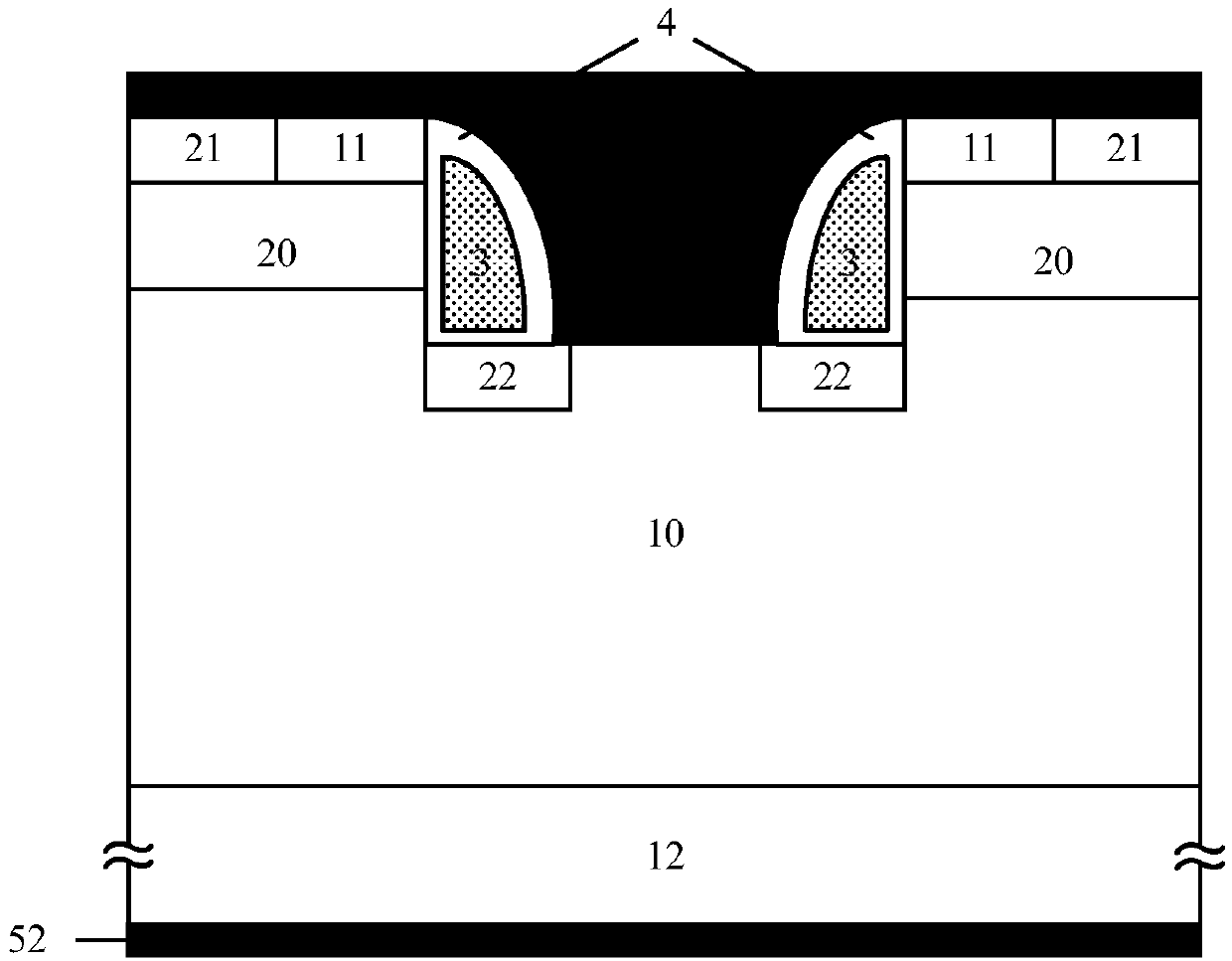

[0034] Such as image 3 As shown, the difference between the device structure of this embodiment and Embodiment 1 is that a P-type contact region 23 at the bottom of the groove is provided between the P-shield regions 22 at the bottom of the groove, and the P-type contact region 23 at the bottom of the groove is in phase with the P-shield region 22. The metal electrode 51 forms a Schottky contact at the gap between the P-type contact region 23 and the P-shield region 22 at the bottom of the trench.

Embodiment 3

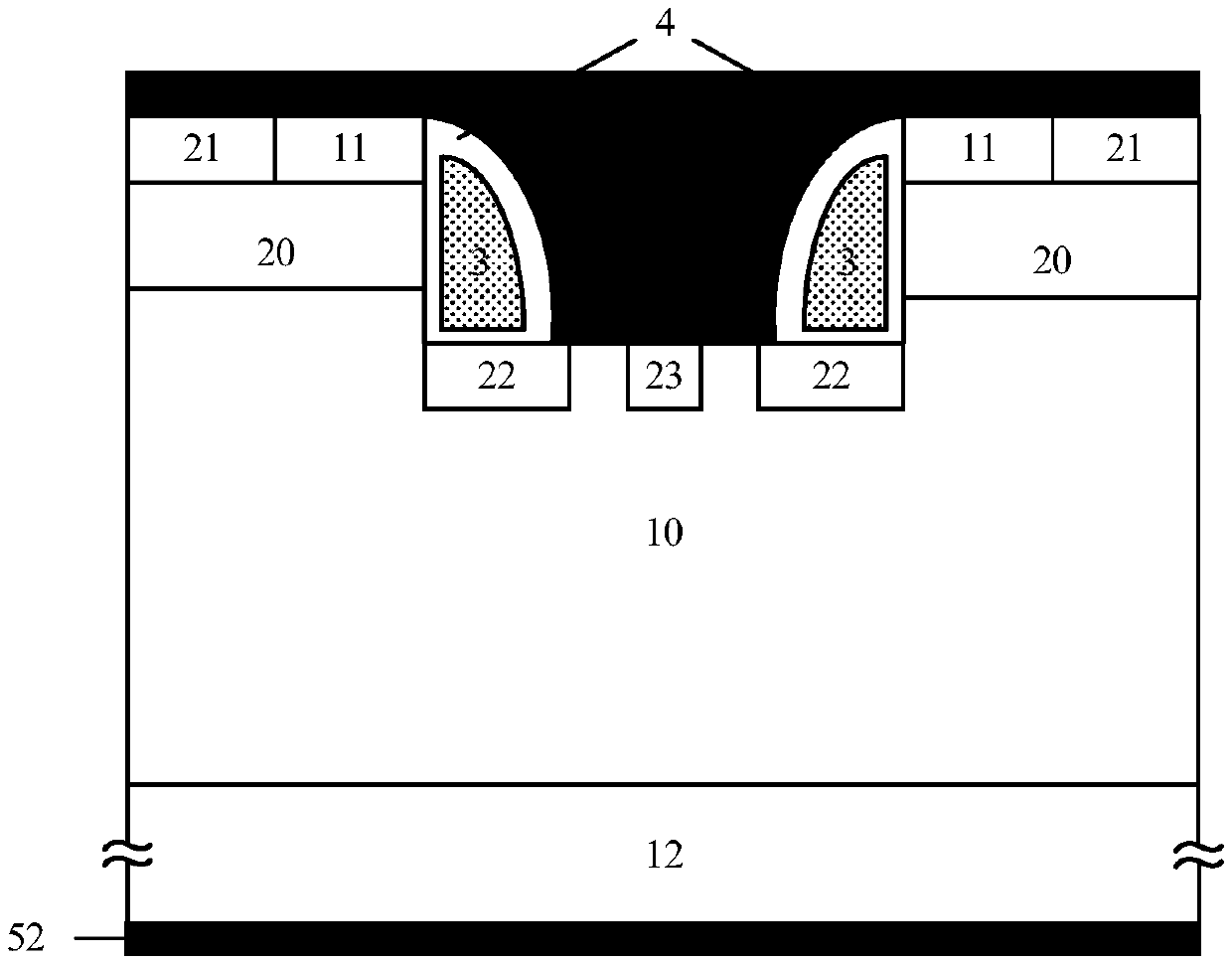

[0036] Such as Figure 4 As shown, the main difference between this embodiment and Embodiment 1 is that the P-shield region 22 at the bottom of the trench is a plurality of separate sub-regions.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com