Manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor devices, electrical solid devices, electrical components, etc., can solve problems affecting device performance, contour and depth anomalies, etc., to ensure contour and depth, ensure performance, and avoid sparse/dense loads. effect of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

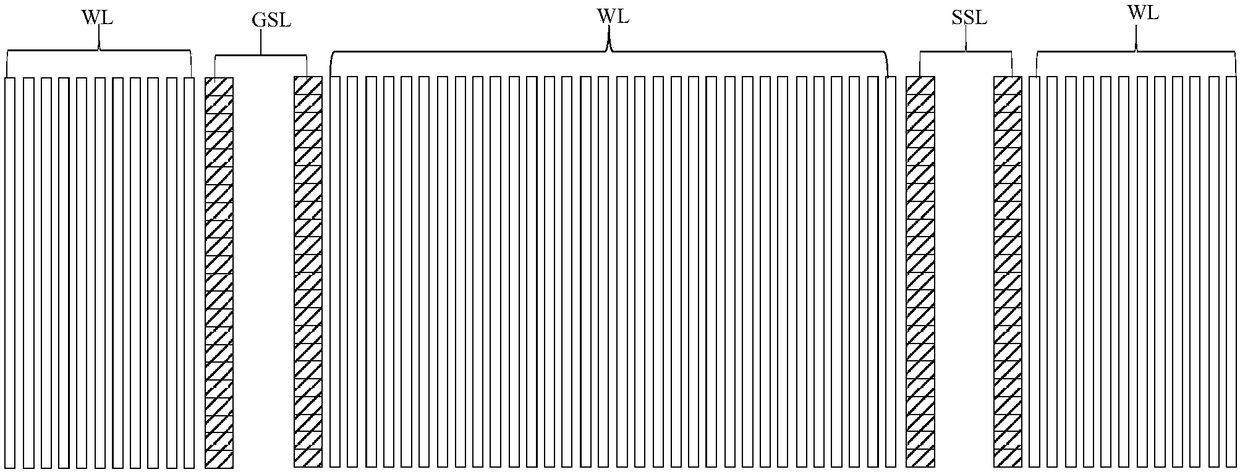

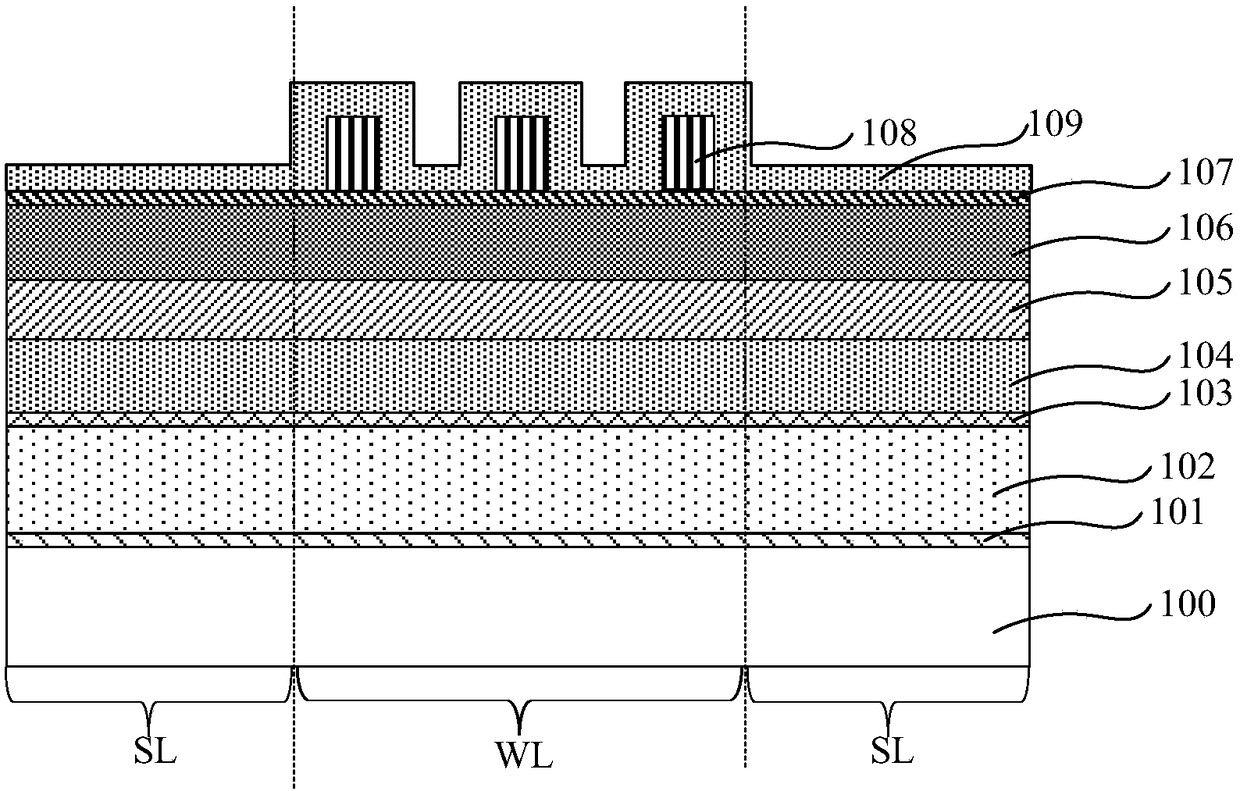

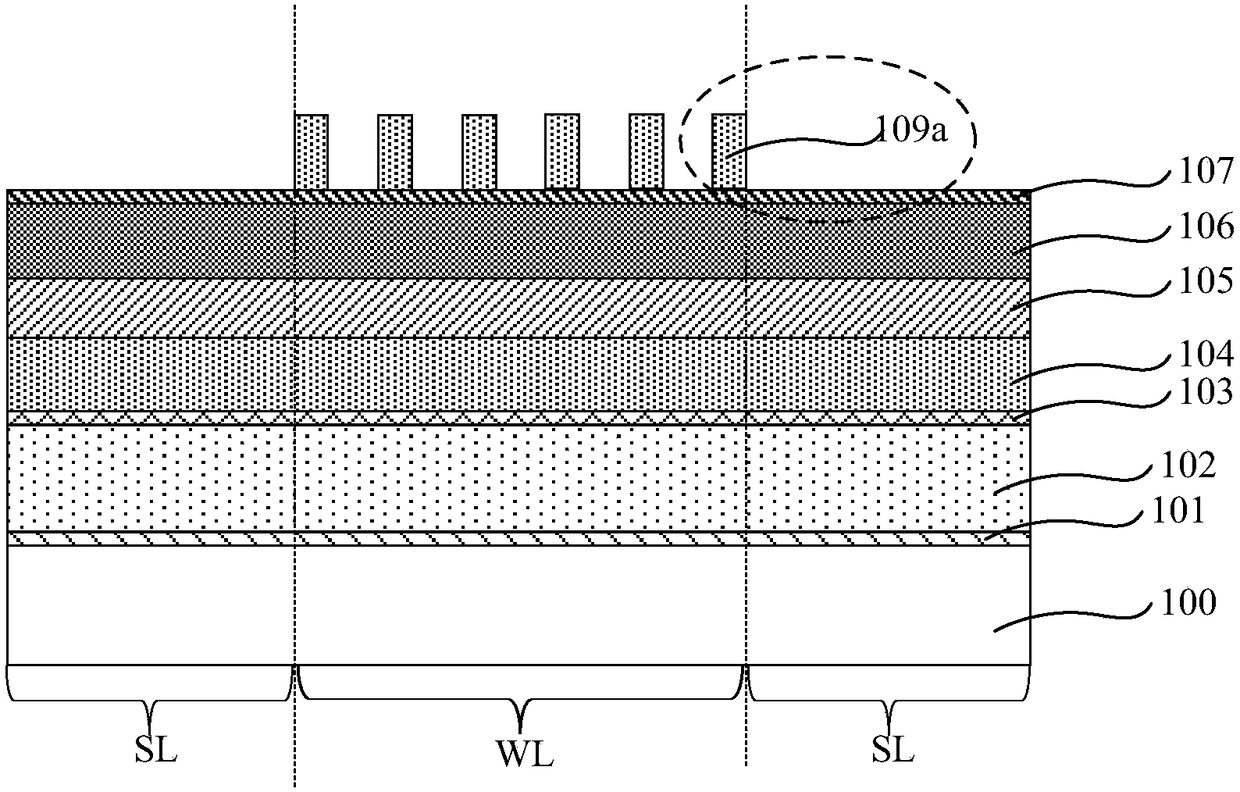

[0037] like figure 1 As shown, the NAND flash memory device may include: a plurality of parallel active regions (ACT, not shown) in a semiconductor substrate separated by a device isolation layer, a ground select gate line (GSL), a string select gate line (SSL) and a plurality of word lines (WL) arranged between adjacent GSLs and SSLs, the GSLs are formed by connecting the gates of the ground selection transistors together, and the sources or drains of these ground selection transistors are connected to the source lines ( SL), SSL is formed by connecting the gates of string selection transistors together, and the source or drain of these string selection transistors is connected to the bit line (BL), and WL is connected by the control gates of the memory cells on the same active area. Formed together, SSL, GSL, WL are arranged in parallel and cross the active region (ACT), and a corresponding charge storage structure can be provided between each WL and each active region (ACT)...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com