A cycle slip suppression circuit for pll frequency synthesizer

A technology of frequency synthesizer and suppression circuit, which is applied in the direction of automatic power control and electrical components, can solve the problems of loop influence and increase the difficulty of implementation, and achieve the effect of small influence, simple control scheme and high integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

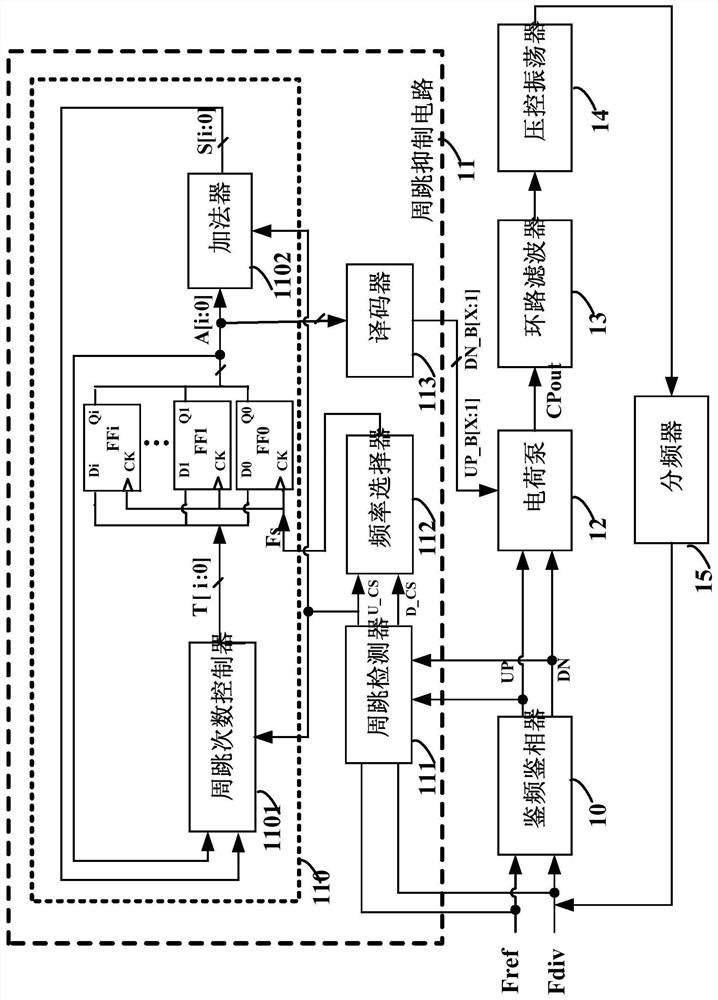

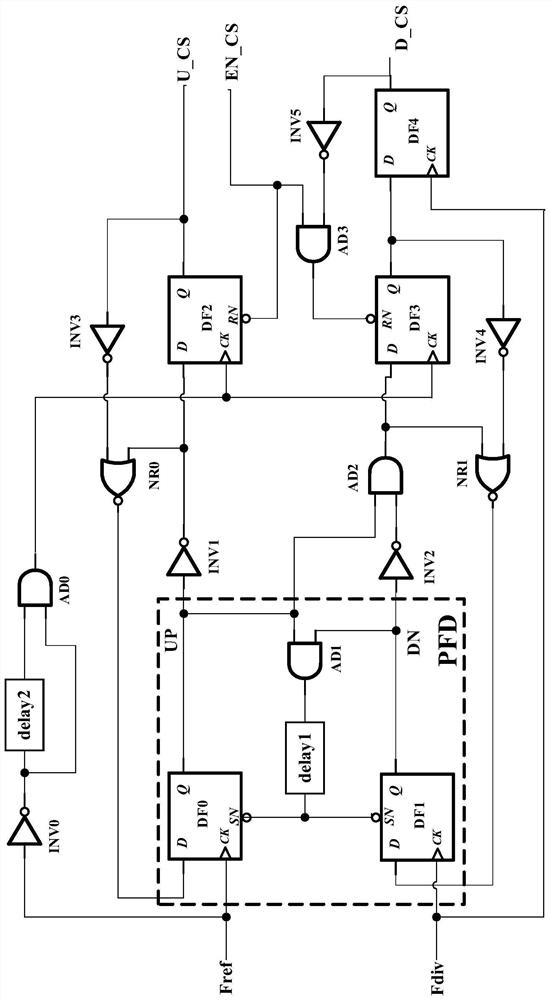

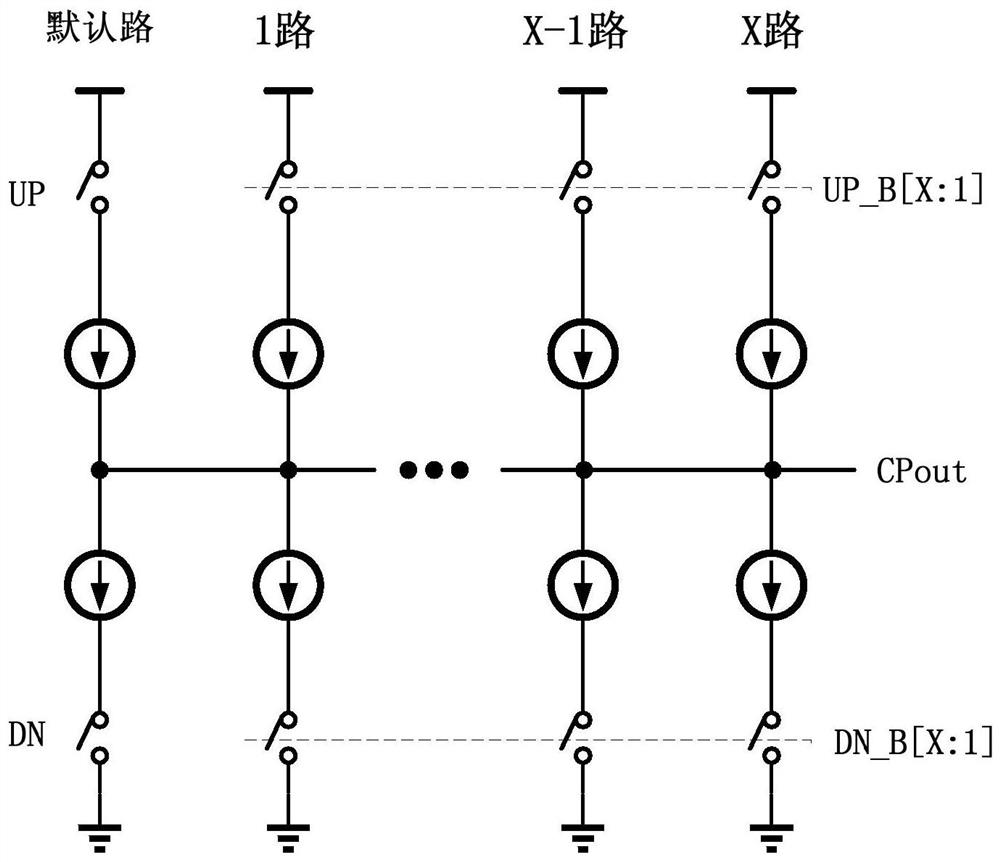

[0029] A charge pump type PLL frequency synthesizer generally includes a phase frequency detector (PFD) 10 , a charge pump 12 , a loop filter 13 , a voltage controlled oscillator 14 and a frequency divider 15 . The input terminals of the PFD are Fref and Fdiv, and the output terminals are UP and DN respectively. The PFD compares the frequency and phase of the input reference signal Fref and the feedback signal Fdiv, and then outputs two signals of UP and DN to select different charging and discharging. The current value CPout is sent to the loop filter, and the loop filter performs low-pass filtering according to the charging and discharging current value CPout output by the charge pump, and then generates a DC voltage and sends it to the voltage-controlled oscillator. The sent DC voltage generates a corresponding output frequency to the frequency divider; the frequency divider divides the output frequency of the voltage-controlled oscillator and feeds it back to the input term...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com