Method for adaptively adjusting data stream load between DSPs (Digital Signal Processor)

A self-adaptive adjustment and data flow technology, applied in the field of signal processing, can solve problems such as data packet time interval becoming smaller, program crashes, data stacking, etc., and achieve the effect of reducing the probability of transmission failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

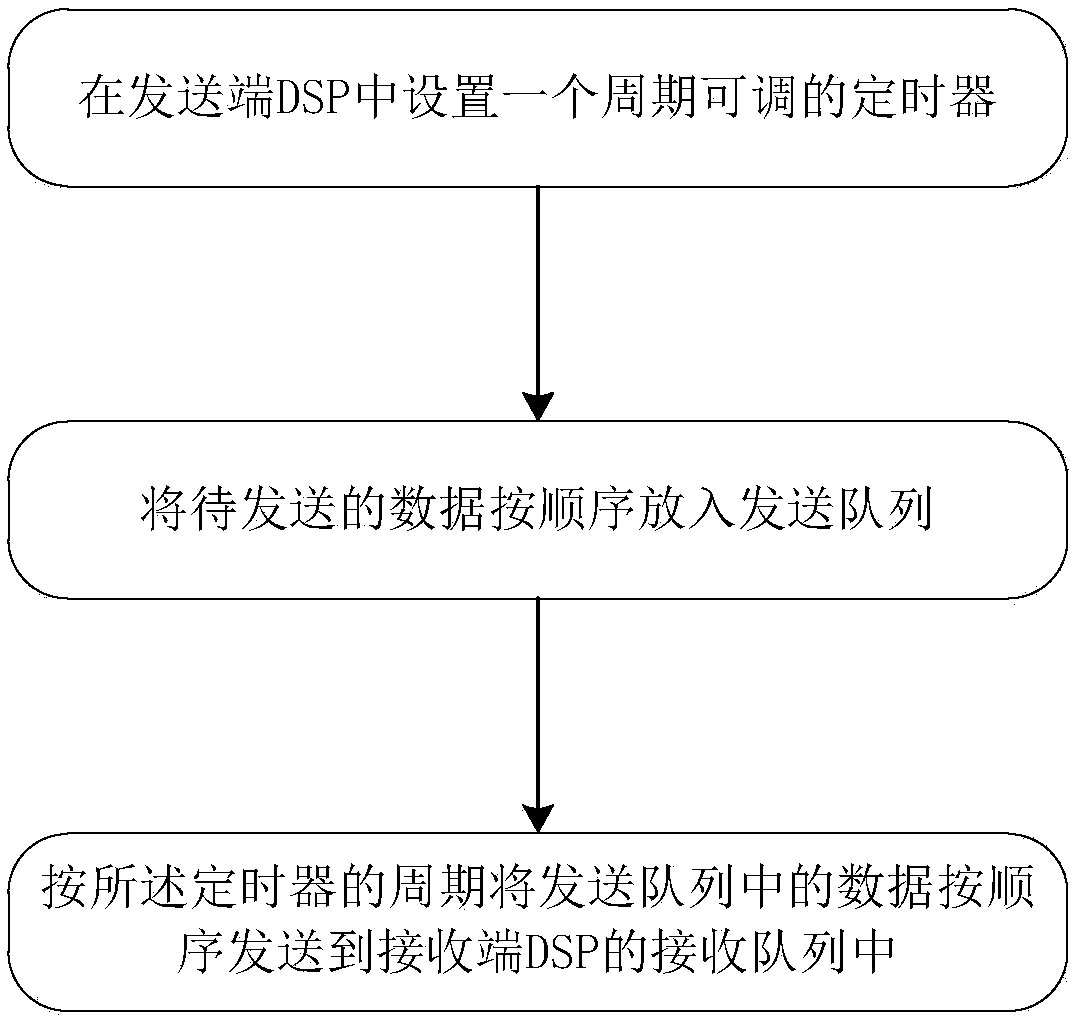

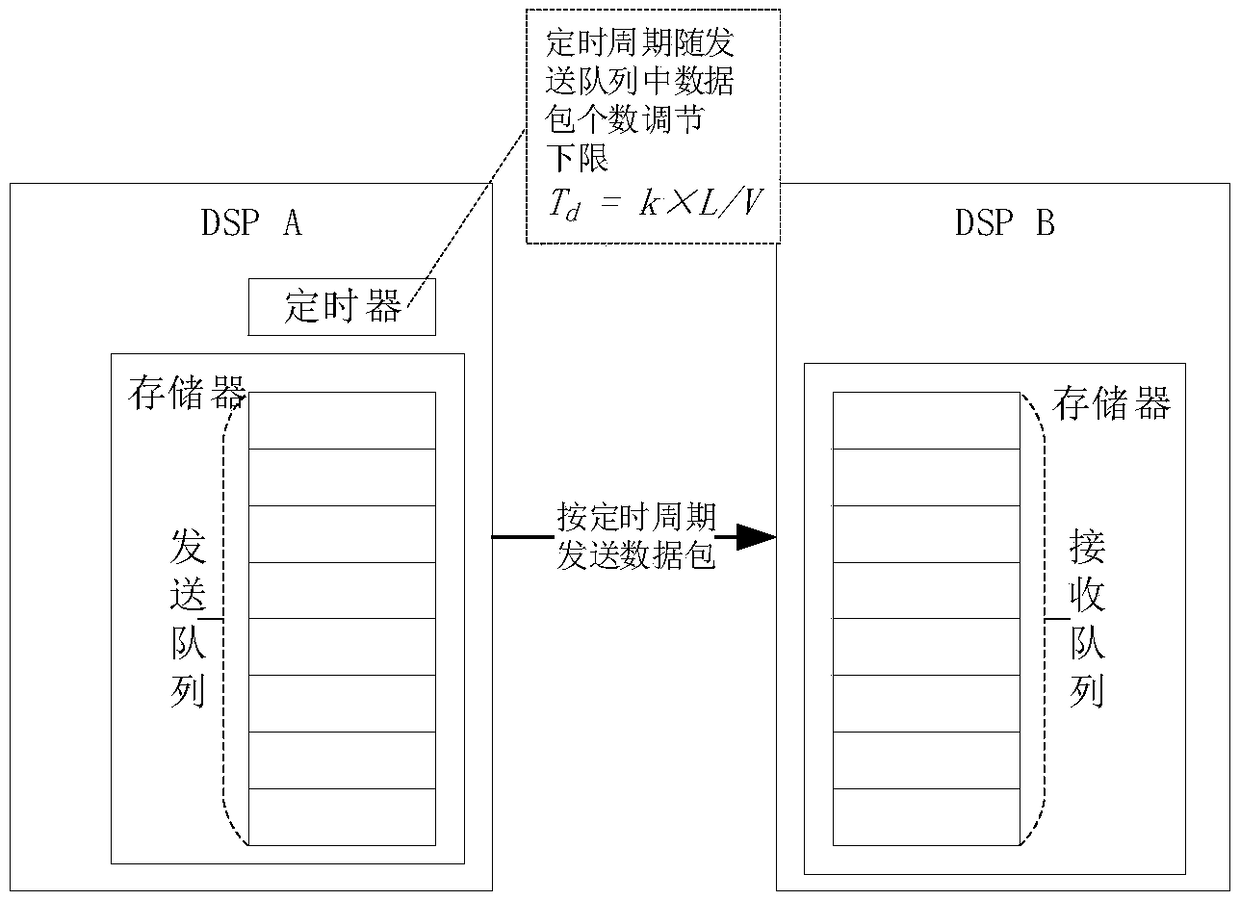

[0030] Take data transmission between two TMS320C6678 as an example. One piece of TMS320C6678 (hereinafter referred to as DSP A) to another piece of TMS320C6678 (hereinafter referred to as DSP B) uses HyperLink to send data close to full load, the steps are as follows:

[0031] 1) Start a timer with adjustable timing period in DSP A, which is used as a metronome for data transmission;

[0032] 2) In the external memory DDR3 of DSP B, create a FIFO (First In First Out) queue with a queue depth of 8, and DSP B puts all received data packets into the receive queue;

[0033] 3) In the memory or external storage of DSP A, create a FIFO (first in first out) queue with a queue depth of 8. DSP A puts all the data packets to be sent into the sending queue; the data packets are only when the queue is not full It can be put in the queue, otherwise it will wait. When the waiting time exceeds the limit value, the data packet will be discarded;

[0034] 4) When the timer interrupt in DSP A is trig...

Embodiment 2

[0039] Take data transmission between two ADSP-TS201 as an example. One piece of ADSP-TS201 (hereinafter referred to as DSP A) to another piece of ADSP-TS201 (hereinafter referred to as DSP B) uses Link to send data close to full load. The steps are as follows:

[0040] 8) Start a timer with adjustable timing period in DSP A, which is used as a metronome for data transmission;

[0041] 9) In the external storage SDRAM of DSP B, establish a FIFO (First In First Out) queue with a queue depth of 10, and DSP B puts all received data packets into the receive queue;

[0042] 10) In the memory or external storage of DSP A, create a FIFO (first in first out) queue with a queue depth of 10, and DPA puts all data packets to be sent into the sending queue; data packets can only be sent when the queue is not full Put it in the queue, otherwise wait, when the waiting time exceeds the limit, discard the data packet;

[0043] 11) When the timer interrupt in DSP A is triggered, that is, when the bea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com