Gallium-nitride transistor employing gap-type composite passivation medium and manufacturing method

A manufacturing method and gap-type technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of device reliability failure, increase leakage current, etc., achieve reduced gate leakage, good effect, and simple process Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

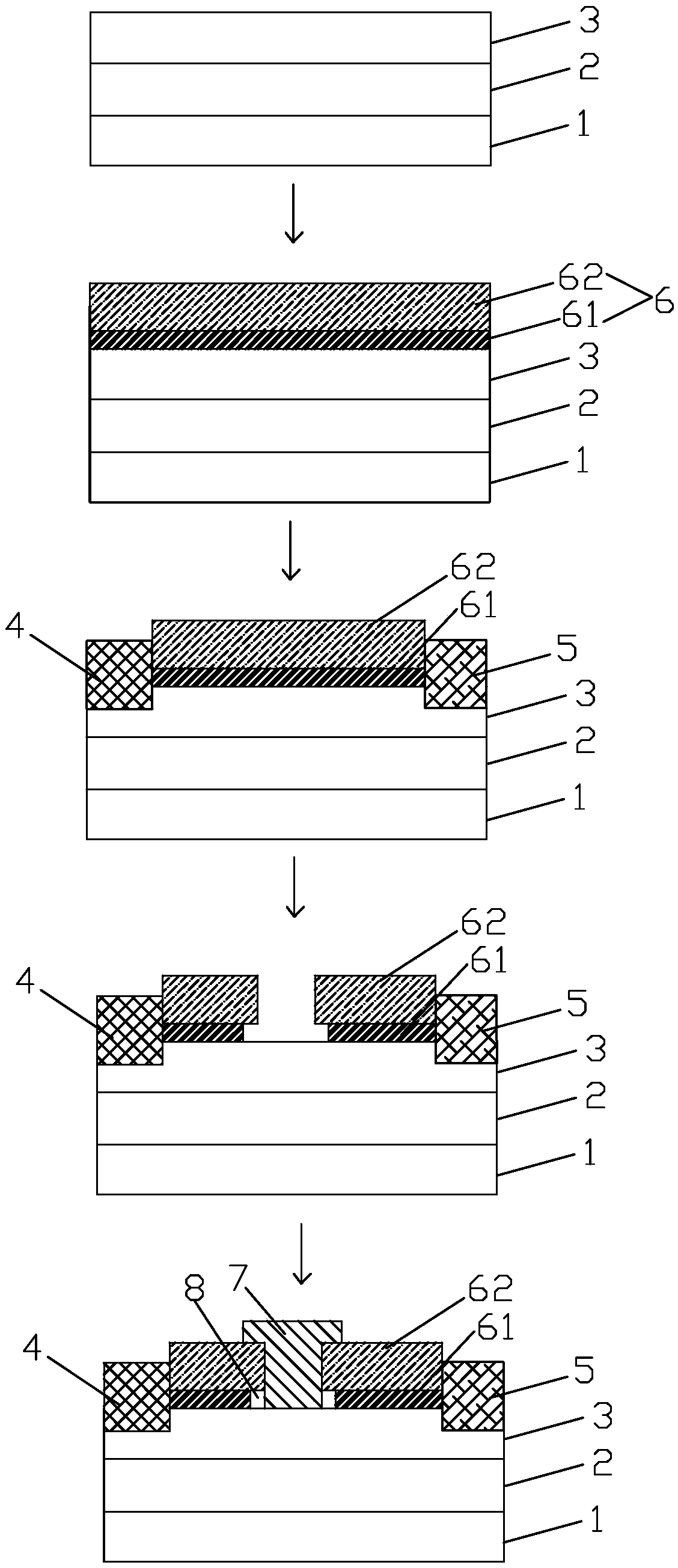

[0029] refer to figure 1 , the production method of this embodiment is as follows:

[0030] 1) An epitaxial layer is provided, and the epitaxial layer includes a substrate 1 , a gallium nitride layer 2 and a barrier layer 3 sequentially stacked from bottom to top. The substrate 1 may be silicon (Si), silicon carbide (SiC), or sapphire (Saphhire), and the barrier layer 3 may be aluminum gallium nitride.

[0031] 2) The isolation region is formed by mesa isolation or ion implantation planar isolation technology, and the source electrode 4 and the drain electrode 5 in ohmic contact with the barrier layer 3 are formed by conventional methods;

[0032] 3) Deposit SiN on the surface of the barrier layer 3 by PECVD after cleaning x For the dielectric, the lower dielectric layer 61 is first formed by using the growth condition with higher Si content, and then the upper dielectric layer 62 is formed by using the growth condition with higher N content. The lower dielectric layer 61 an...

Embodiment 2

[0037] The production method of this embodiment is as follows:

[0038] 1) With reference to Example 1.

[0039] 2) After cleaning, deposit SiOx medium on the surface of the barrier layer by PECVD method to form the lower dielectric layer, and then deposit AlO on the lower dielectric layer by ALD method x An upper dielectric layer is formed, and the lower dielectric layer and the upper dielectric layer form a composite passivation dielectric layer.

[0040] 3) using Cl-containing plasma to etch the upper dielectric layer, and then using F-based plasma to etch the lower dielectric layer, thereby forming a window on the composite passivation dielectric layer, and controlling the window width of the lower dielectric layer to be greater than that of the upper dielectric layer by controlling the etching time medium layer. The Al-based medium is etched with Cl-containing plasma, which has a relatively fast etching rate, and the F-based plasma is basically etched without moving; on...

Embodiment 3

[0044] The production method of this embodiment is as follows:

[0045] 1) With reference to Example 1.

[0046] 2) After cleaning, an Al-based dielectric is deposited on the surface of the barrier layer to form a lower dielectric layer, and then a Si-based dielectric is deposited on the lower dielectric layer to form an upper dielectric layer, and the lower dielectric layer and the upper dielectric layer form a composite passivation dielectric layer.

[0047] 3) Etching the upper dielectric layer with F-based plasma, and then wet-etching the lower dielectric layer with an alkaline solution to form a window on the composite passivation dielectric layer, and controlling the window width of the lower dielectric layer to be larger than the upper dielectric layer by controlling the etching time layer. The wet etching process has almost no etching effect on the Si-based dielectric.

[0048] 4) Referring to Example 1, a gallium nitride transistor with a gap-type composite passivat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com