Automatic generation method for customizable logic device layout and netlist

A technology of automatically generating and customizing logic, applied to instruments, special data processing applications, electrical digital data processing, etc., can solve problems such as not supporting user customization, costing a lot of repetitive time, and disadvantageously seizing the market, so as to reduce a lot of workload, Convenience for structural analysis and quick launch

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The present disclosure provides a method for automatically generating a customizable logic device layout and netlist, which supports user customization, and is simple in operation, fast in speed, capable of batch processing, and strong in scalability, helping to reduce back-end The large workload of the layout personnel facilitates the structural analysis of the software engineers, and facilitates the rapid launch of the chips and seizes the market.

[0033] In order to make the purpose, technical solutions and advantages of the present disclosure clearer, the present disclosure will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0034] In a first exemplary embodiment of the present disclosure, a method for automatically generating a customizable logic device layout and netlist is provided.

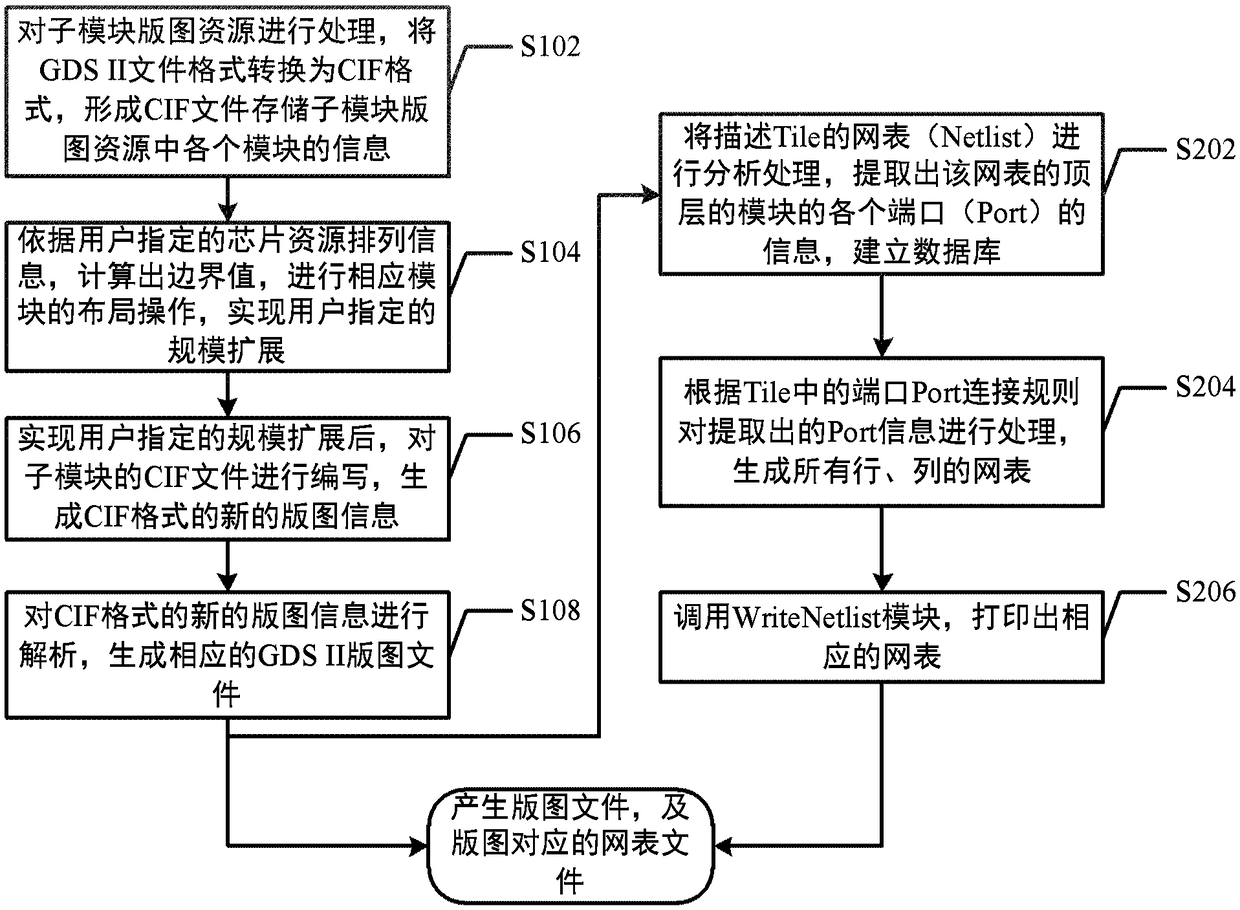

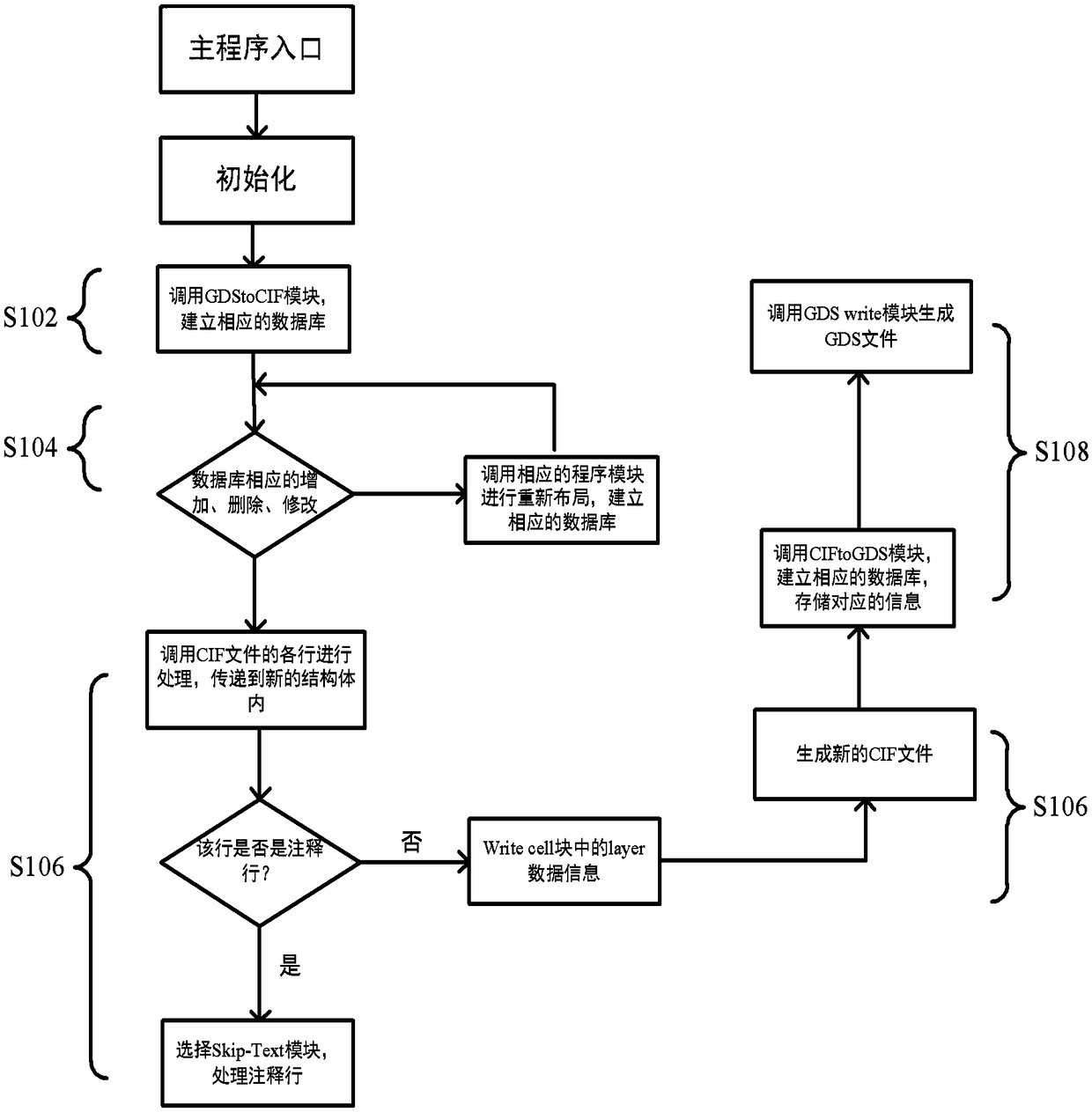

[0035] figure 1 It is a flowchart of a method for automatically generating a layout of a customiz...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com