Data compressed SoC chip information tracking device and performance optimization method

A technology of information tracking and data compression, which is applied in the fields of electrical digital data processing, instruments, hardware monitoring, etc., can solve the problem of large data volume, increased SoC area and power consumption, default bus access priority and bandwidth arrangement are not optimal and other issues to achieve the effect of improving efficiency and reducing memory usage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described below in conjunction with accompanying drawing.

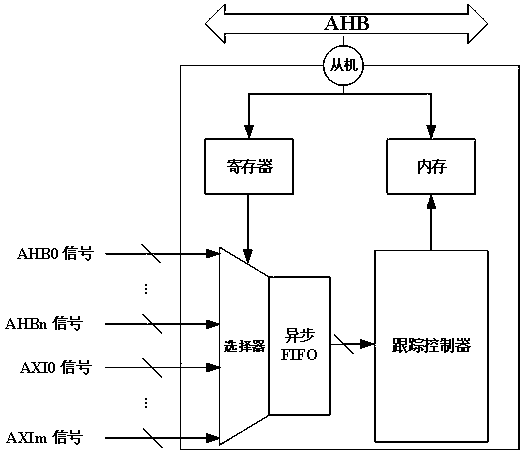

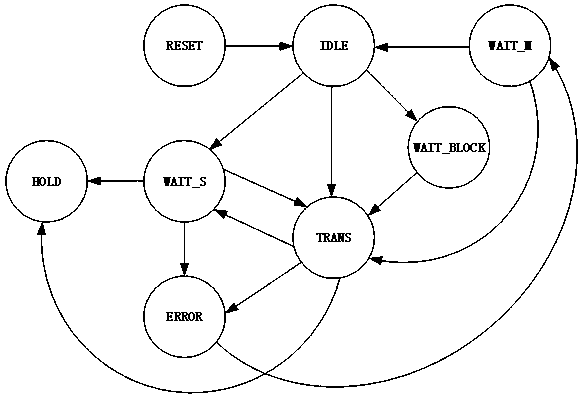

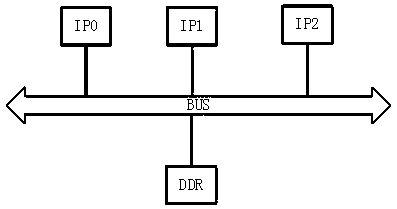

[0022] The main purpose of the present invention is to adopt the data compression method to track the bus access delay, bus transmission data, bus transmission bandwidth, etc. in the SoC without affecting the normal operation of the SoC, so as to facilitate the debugging of bus device problems and optimize the bus structure. Among them, the record of the bus access delay state indicates the condition of the host occupying the bus and the response of the bus to each host request, reflecting whether the setting of the bus access priority is reasonable. The record of bus transmission data represents the read and write data of each host, which is convenient for data tracking and error location in system-level debugging. The record of bus transmission bandwidth indicates the data throughput rate of each host, such as image 3 It is convenient to adjust the access priority accor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com