Data flow instruction mapping method

A mapping method and data flow technology, applied in the direction of concurrent instruction execution, electrical digital data processing, program control design, etc., can solve problems affecting the execution efficiency of data flow programs, generating a large number of routing packets, and on-chip network congestion, etc., to improve execution Efficiency, reducing the effect of on-chip network congestion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

[0059] The computing unit array in this example constitutes a Mesh grid. The routing algorithm of the on-chip network is X-Y routing, that is, X-axis routing first, and then Y-axis routing. At the same time, the on-chip network transmission routing packet is a multi-address shared data routing packet structure.

[0060] The data flow graph traverses the sub-steps:

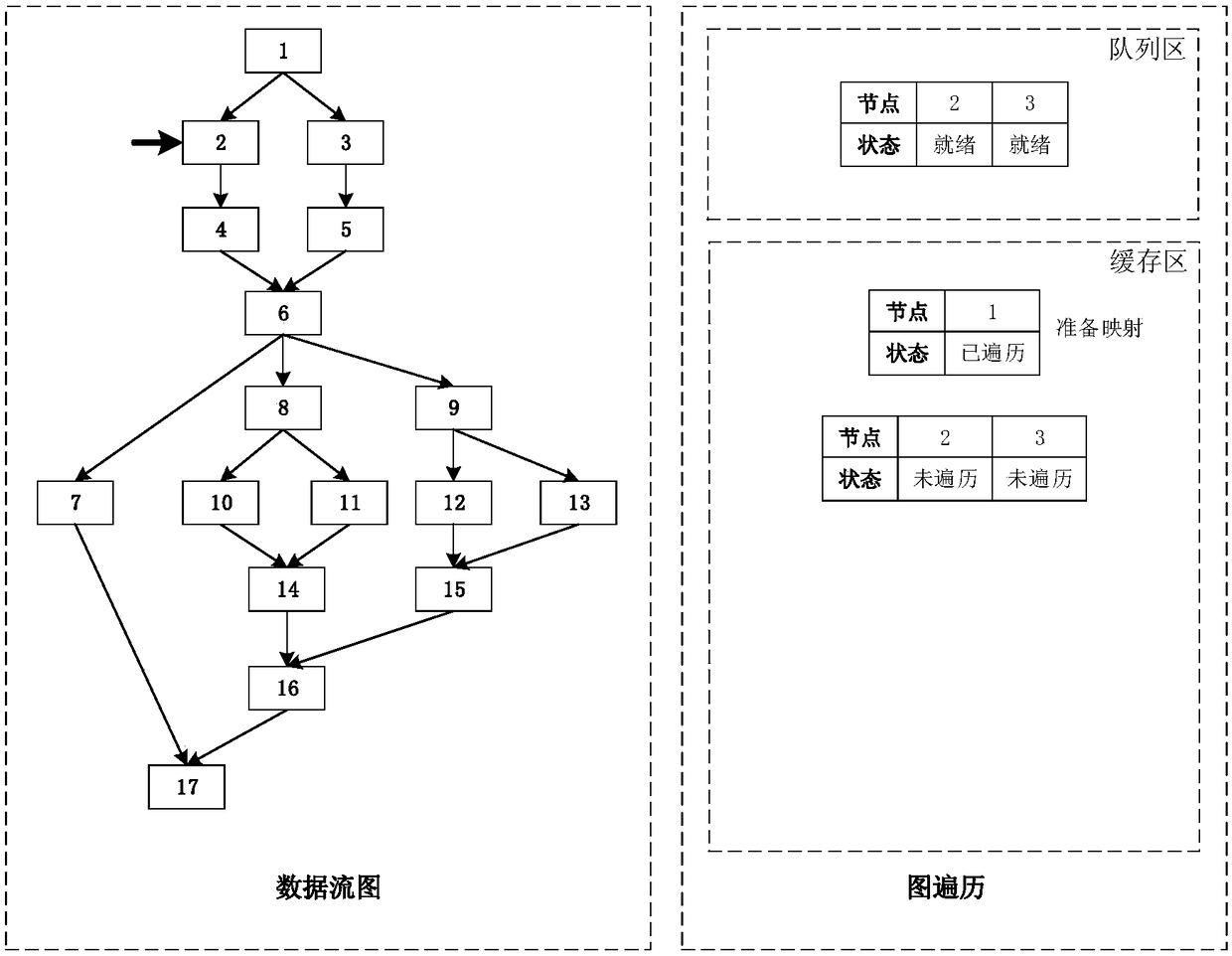

[0061] Step 101: The data flow graph traverses the initial state such as figure 1 As shown, the traversal process has two areas, one is the queue area, which is similar to the breadth-first traversal priority queue of the graph, and is used to record the nodes that need to be traversed next, and the other is the buffer area, which is used to record whether the binding instruction is It can be mapped, and a "bundle instruction" refers to "at least two downstream instructions located downstream of the same data flow instruction". In this figure, the initial traversal is node 1 of the data flow graph, so the queue ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com