Display backplane and manufacturing method thereof, display panel and display device

A technology for displaying backplanes and substrates, which is applied to electrical components, electric solid-state devices, circuits, etc., and can solve problems such as the structural design of array substrates needs to be improved, it is difficult to realize, and the light-emitting area is reduced.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0086] The following describes the embodiments of the present invention in detail, and those skilled in the art will understand that the following embodiments are intended to explain the present invention, and should not be regarded as limiting the present invention. Unless otherwise specified, in the following examples that do not explicitly describe specific techniques or conditions, those skilled in the art can carry out according to commonly used techniques or conditions in this field or according to product instructions.

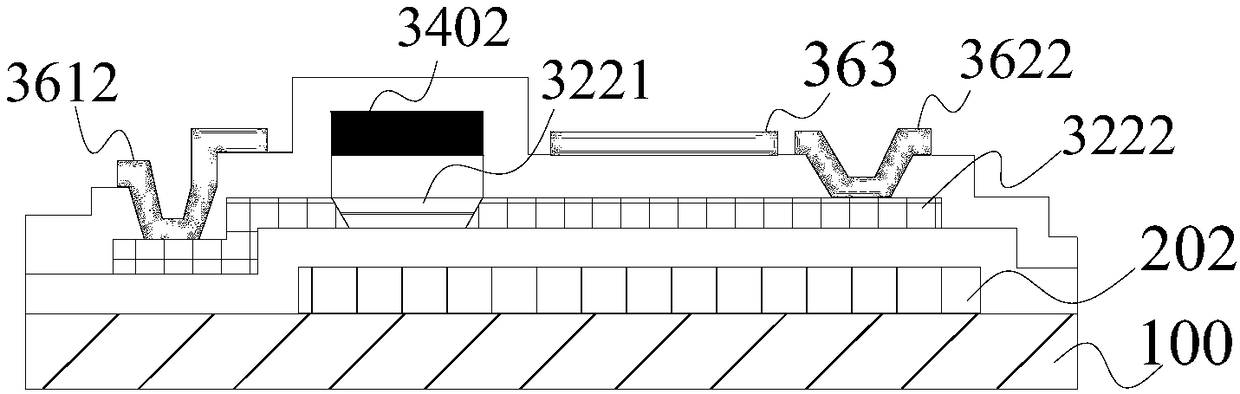

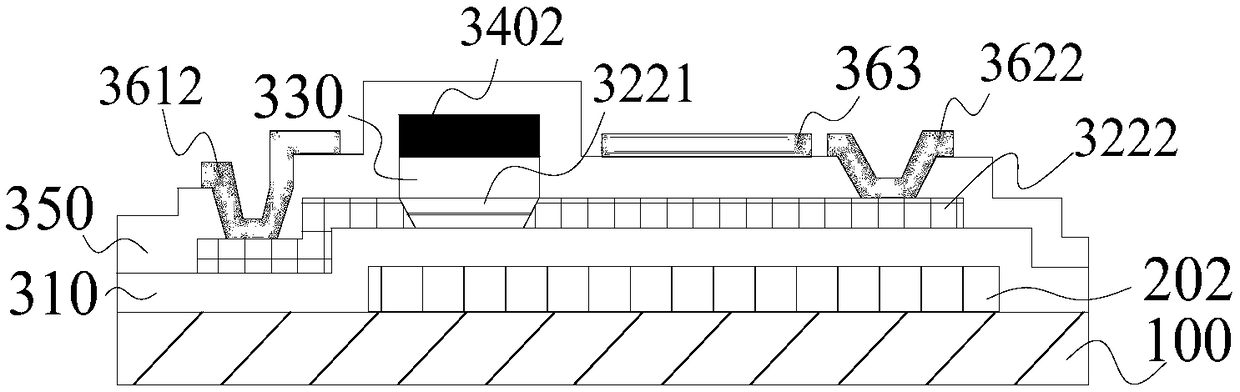

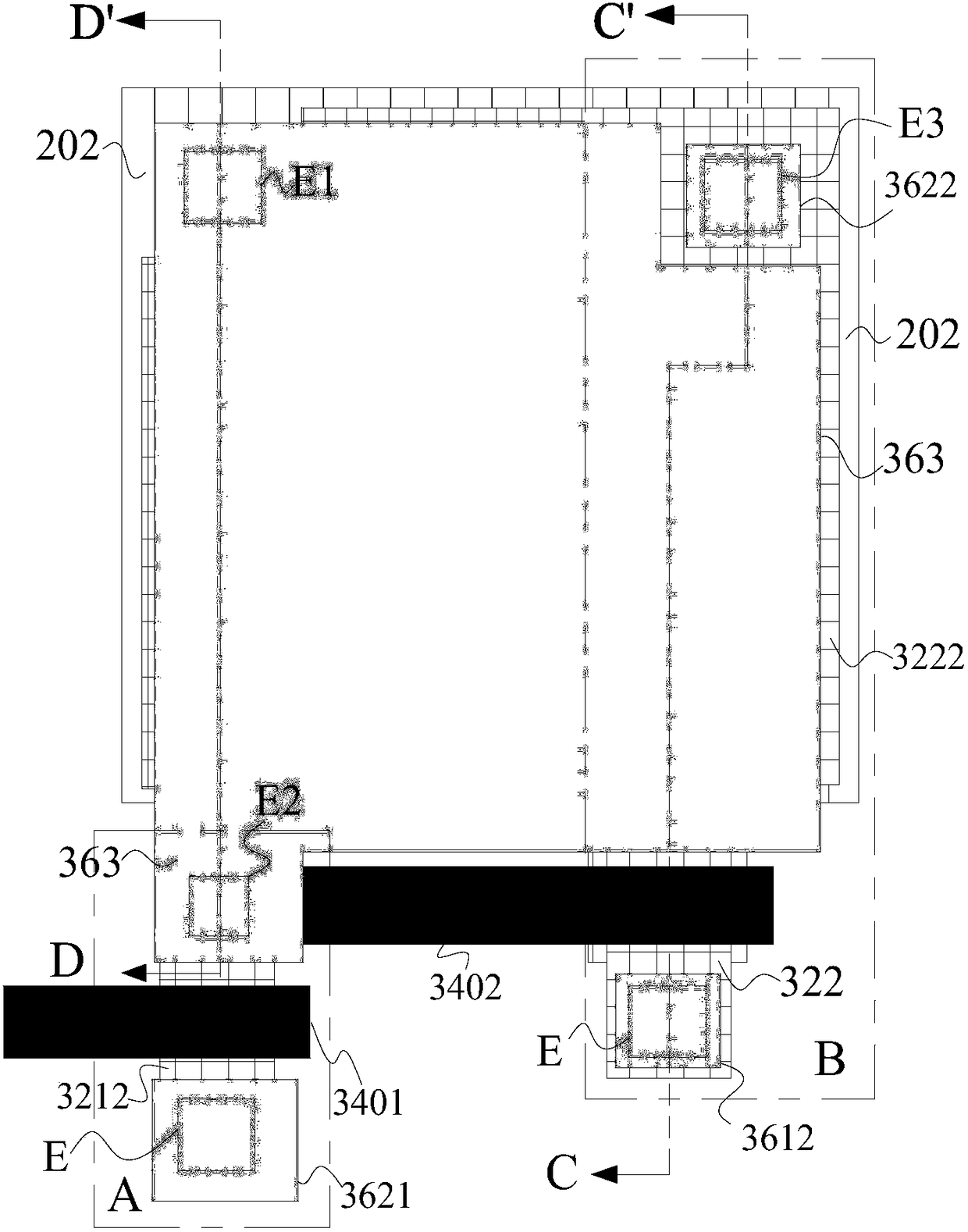

[0087] In one aspect of the invention, the invention provides a display backplane. refer to Figure 1~5 , 8-19, the display backplane of the present invention is described in detail. It should be noted that in this paper, Figure 1~2 The shown structural diagram of the display backplane is a schematic diagram of the cross-sectional structure along the direction of the driving TFT (DR tube) from the drain (D) to the source (S), and image 3 , 8 11, 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com