SoC chip-based deep neural network embedded realization method

A technology of deep neural network and implementation method, applied in the field of airborne intelligent computing, can solve problems such as poor flexibility, long verification period, and very difficult timing design, and achieve the effect of improving flexibility, reducing size and power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

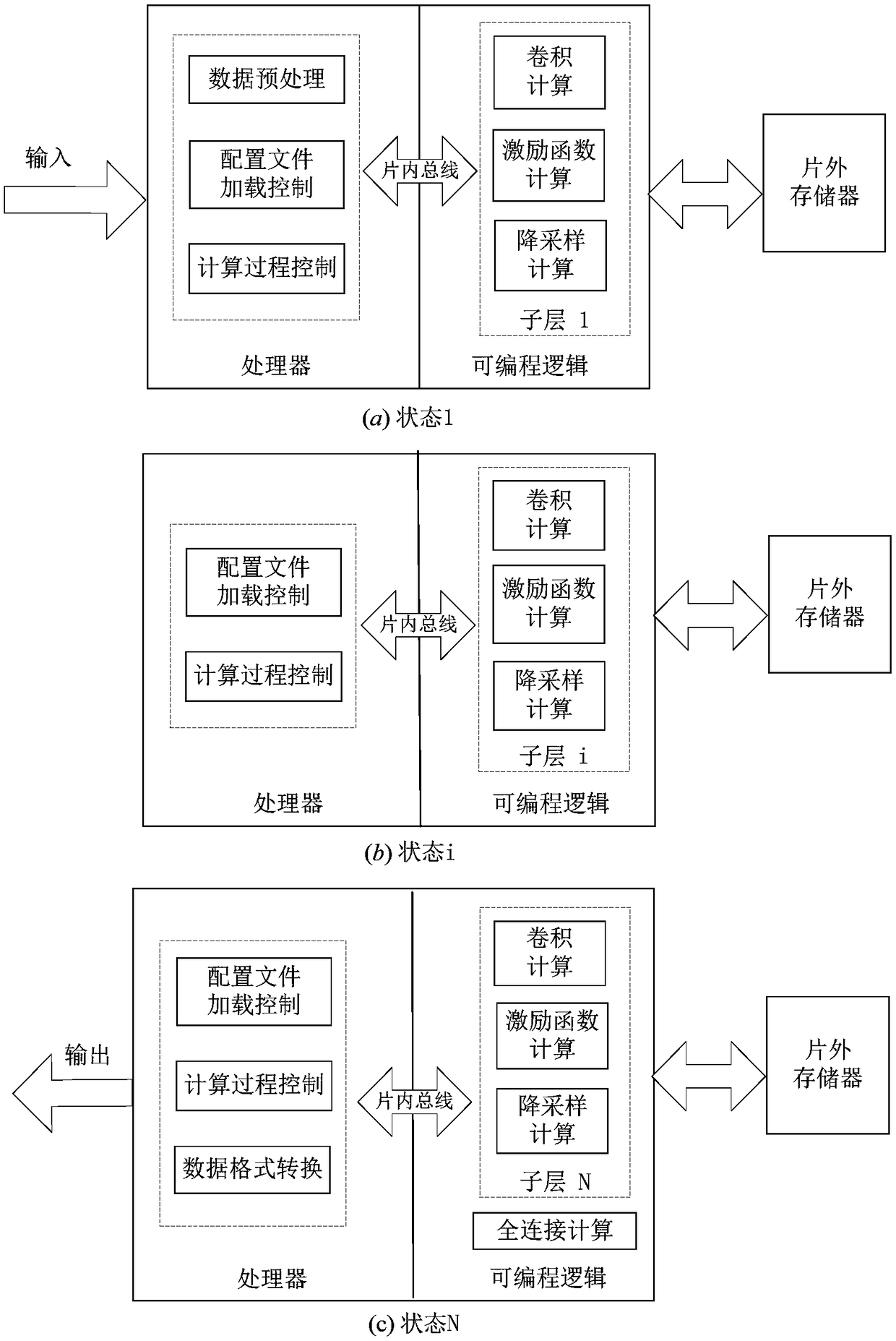

[0015] See attached figure 1 The present invention is described in further detail.

[0016] The method is implemented based on the SoC chip. The main program of the neural network is implemented on the processor core to complete the global scheduling task; the calculation-intensive part is implemented on the programmable logic to complete the parallel computing task; the two parts are controlled by the high-speed bus on the chip. The exchange of state information realizes the cooperative work of the processor and programmable logic; when the deep neural network is running, the input information is transmitted to the SoC chip through the video interface, Ethernet interface, bus interface or storage interface according to the actual situation, and is processed as needed. The image grayscale calculation, data normalization or image segmentation and other preprocessing processes are completed in the processor. At the same time, the processor controls the calculation logic and rel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com