3D packaging structure for mass memory circuit

A technology of large-capacity memory and packaging structure, which is applied in the direction of circuits, electrical components, semiconductor devices, etc., to achieve the effect of increasing storage capacity and meeting high reliability requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

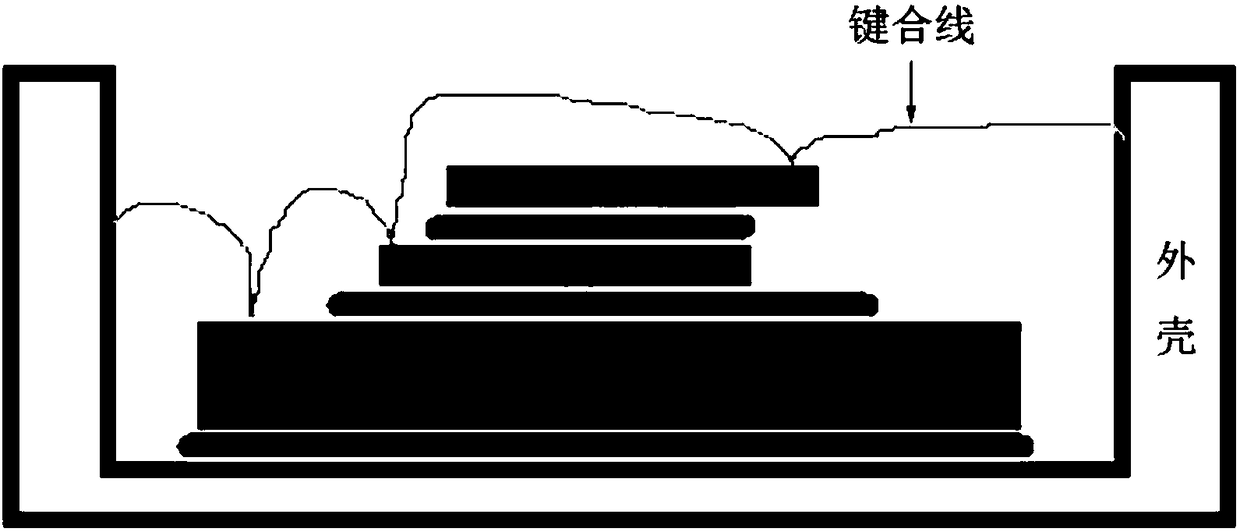

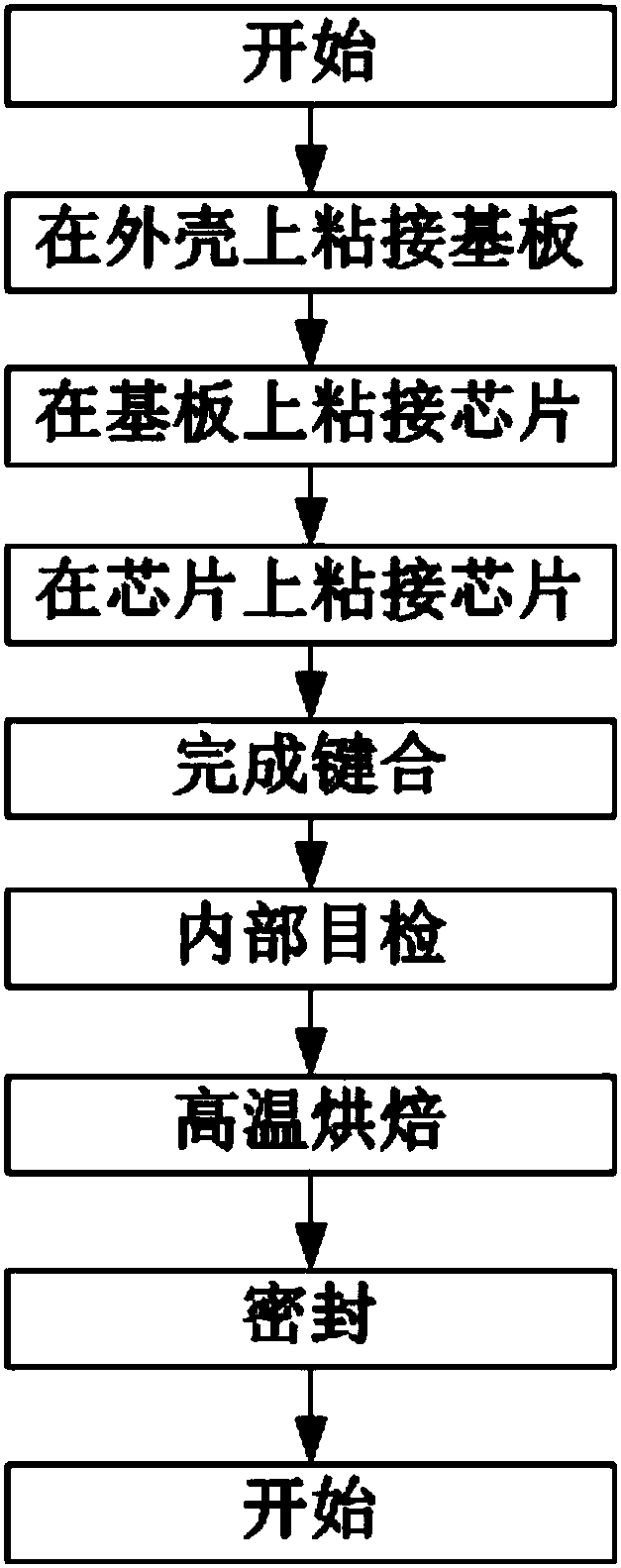

[0031] In this embodiment, the flow of reliable 3D packaging of large-capacity storage circuits is as follows: figure 2 shown. The encapsulation process is as follows:

[0032] A ceramic shell is selected, the shell and the substrate are integrated, and the wiring relationship is completed inside the ceramic shell to replace the independent substrate. The memory chip is a 128Gb Nand Flash memory chip with a chip size of 11mm×15mm. First, apply a proper amount of non-conductive glue inside the tube case, and place a memory chip on the non-conductive glue inside the tube case. Next, continue to apply an appropriate amount of non-conductive glue on the memory chip, and place another memory chip on the non-conductive glue on the memory chip.

[0033] Staggered bonding between the memory chip and the memory chip. After the two chips are vertically aligned and the centers coincide, the second chip moves horizontally 2mm along the X\Y direction to expose the PAD point of the firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com