FPGA-based real-time implementation method for interframe-accumulation and noise-reduction algorithm of low-light video

An implementation method and video frame technology, applied in television, computing, color television, etc., to achieve the effect of reducing storage device capacity requirements and clock frequency requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

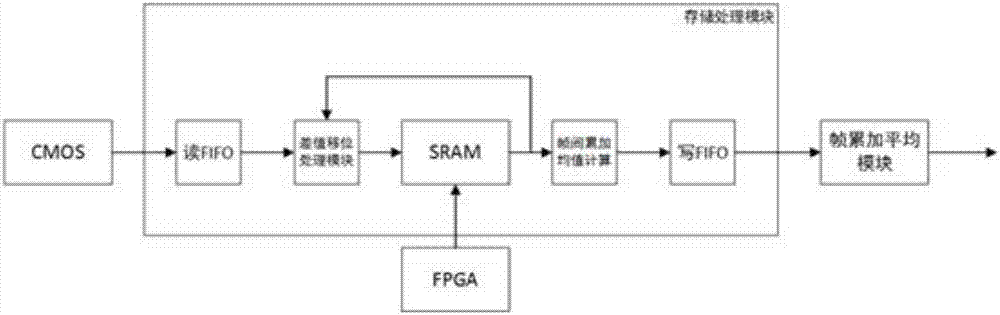

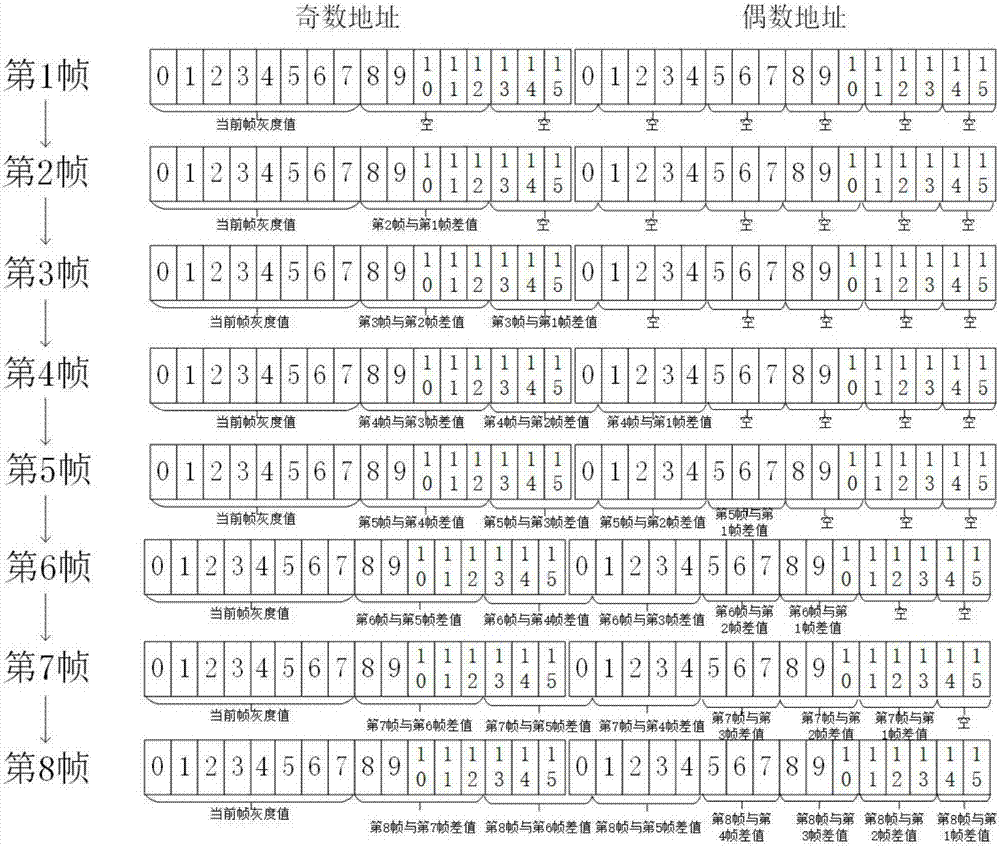

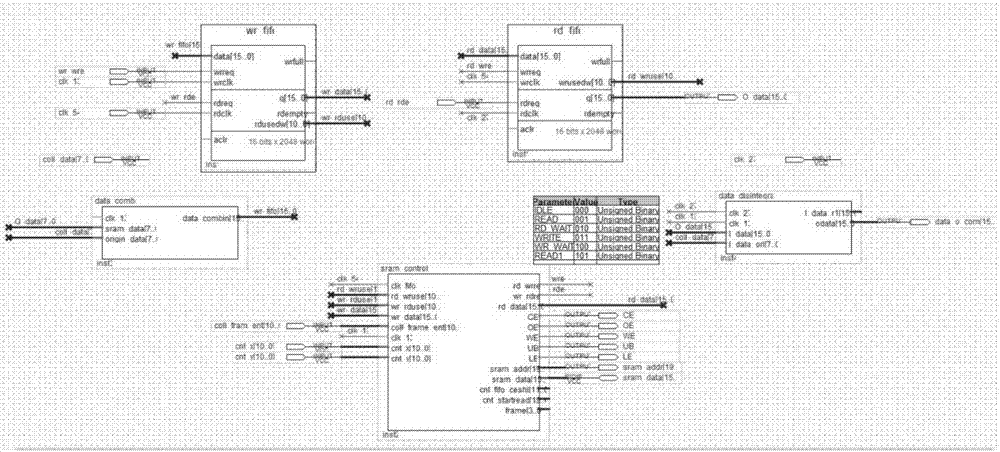

[0014] The purpose of the present invention is to provide a real-time display method for multi-frame accumulated low-light video denoising under the condition that memory storage capacity and clock frequency are relatively scarce. The operation is performed by calculating and storing the difference between the gray value of the corresponding pixel of the multi-frame image and the corresponding pixel of the current frame, using the maximum operable bit width of the storage device, and assigning different bits according to the time distance from the current frame Wide to store the difference between the gray value of the same pixel as the current frame, which saves storage space and reduces the impact on the filtering effect, and finally achieves accumulation under the condition of a small capacity storage space of 13.27Mb and a lower clock frequency of 27MHz Inter-frame accumulative filter noise reduction with 8 frames.

[0015] The operation is performed by calculating and sto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com