Forming method for fin-type field effect transistor

A fin-type field effect transistor and fin technology are applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., to achieve the effect of improving electrical performance and good performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

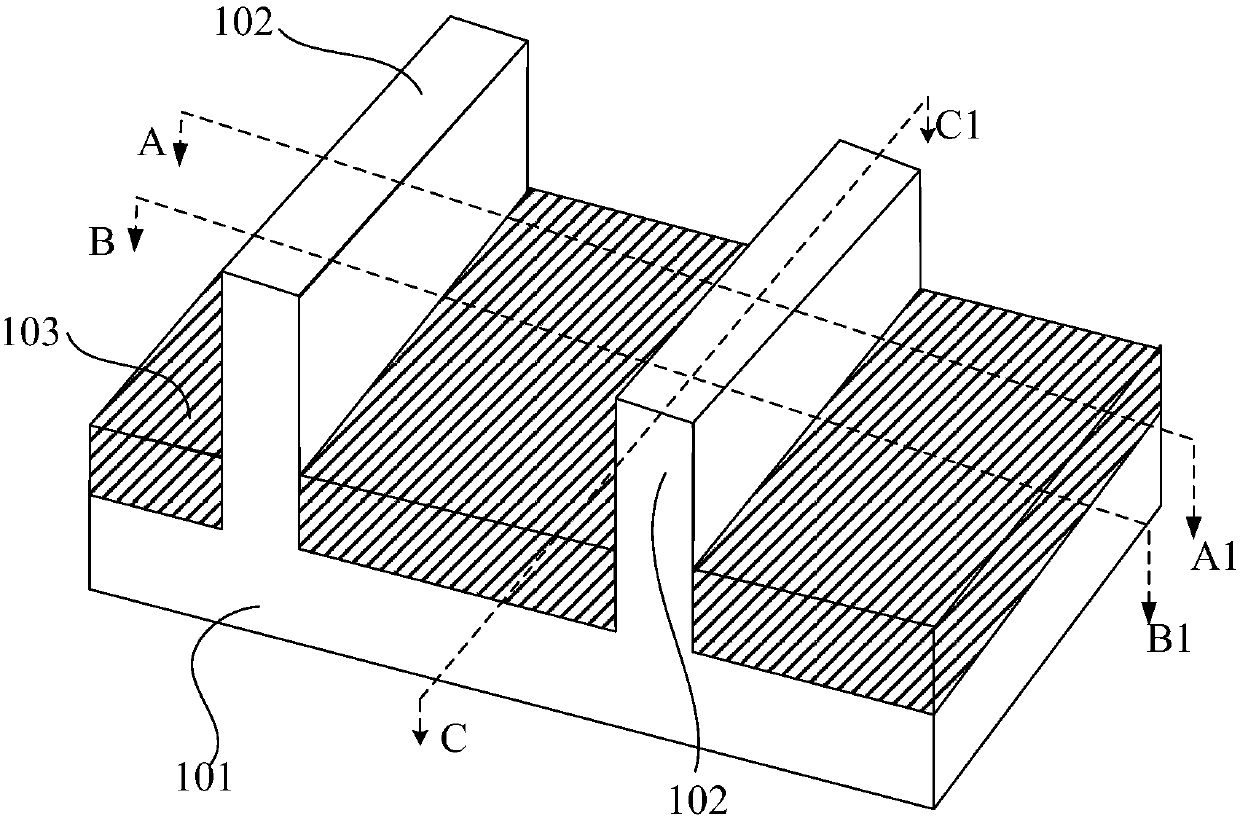

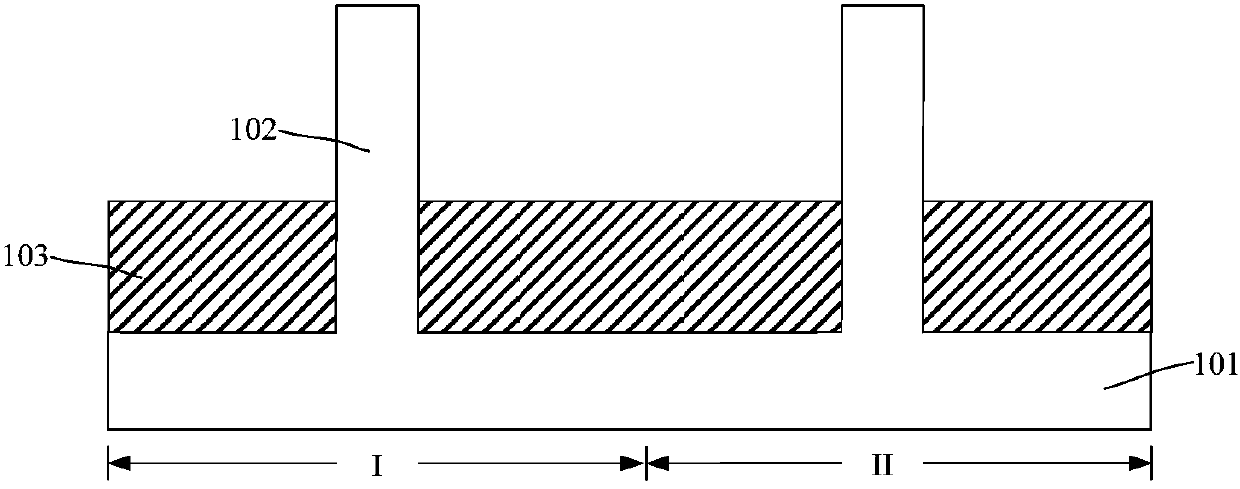

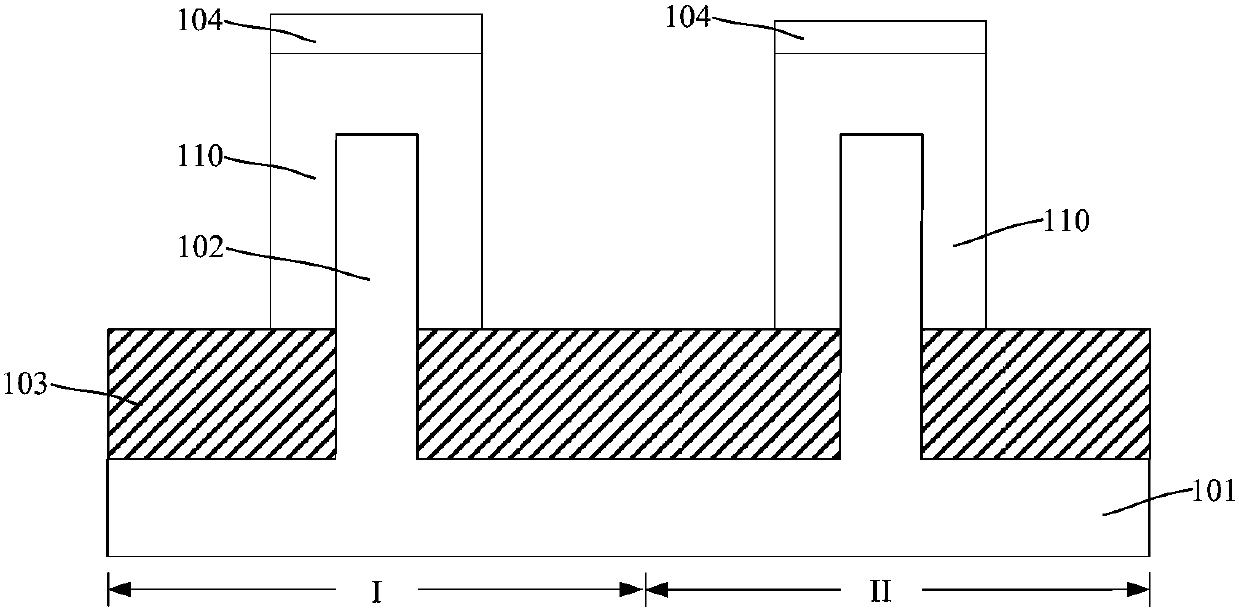

[0032] It can be seen from the background art that the performance of the fin field effect transistor formed in the prior art needs to be further improved, especially the electrical performance of the NMOS fin field effect transistor is poor.

[0033] According to the analysis, the formation process of the NMOS fin field effect transistor includes the steps of: forming a mask side wall on the side wall of the fin in the NMOS region; Forming an N-region groove in the portion; forming an N-type doped epitaxial layer filling the N-region groove. In order to limit the shape and volume of the formed N-region doped epitaxial layer, when etching and removing the fins with partial thickness on both sides of the gate structure in the NMOS region, the mask sidewalls located on the sidewalls of the fins are kept, so that the formed The two opposite sidewalls of the groove in the N region are mask sidewalls; during the process of forming the N-type doped epitaxial layer, the mask sidewall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com