Digital-analog hybrid control multi-loop LDO circuit

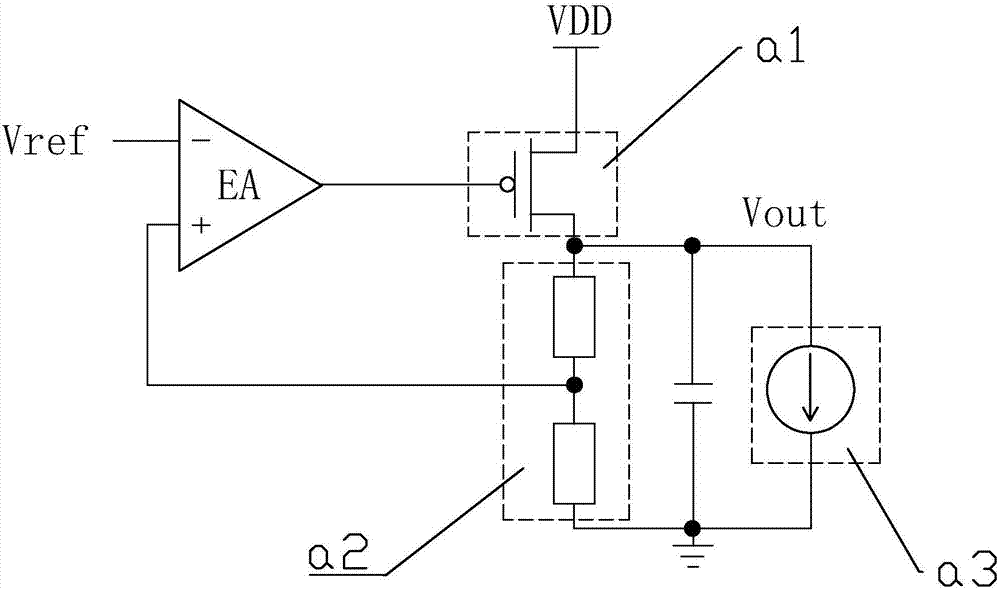

A digital-analog hybrid, multi-loop technology, applied in control/regulating systems, regulating electrical variables, instruments, etc., can solve the problem of low load transient response capability of LDO circuits, and achieve the effect of improving load response speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

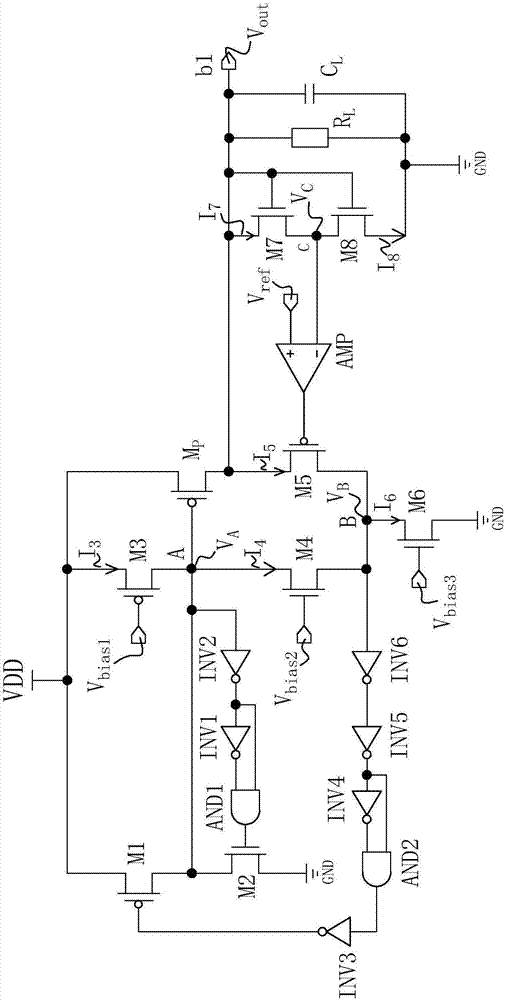

[0014] Embodiment 1, reference figure 2 , a digital-analog hybrid control multi-loop LDO circuit, comprising: power tube M P , pMOS transistors M1, M3, M5, nMOS transistors M2, M4, M6, M7, M8, operational amplifiers AMP, NOT gates INV1, INV2, INV3, INV4, INV5, INV6, AND gates AND1, AND2, the pMOS transistor M1 , M3, power tube M P The sources of are respectively connected to the power supply VDD, as an optimization, where the power tube M P A pMOS transistor is used, the gate of the pMOS transistor M1 is connected to the output terminal of the inverting gate INV3, the input terminal of the inverting gate INV3 is connected to the output terminal of the AND gate AND2, and an input of the AND gate AND2 end is connected with the output terminal of the NOT gate INV4, the other input terminal of the AND gate AND2 is connected with the input terminal of the NOT gate INV4 and the output terminal of the NOT gate INV5 respectively, and the input terminal of the NOT gate INV4 end is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com