A charge-transfer analog counting readout circuit based on pulse rising edge trigger

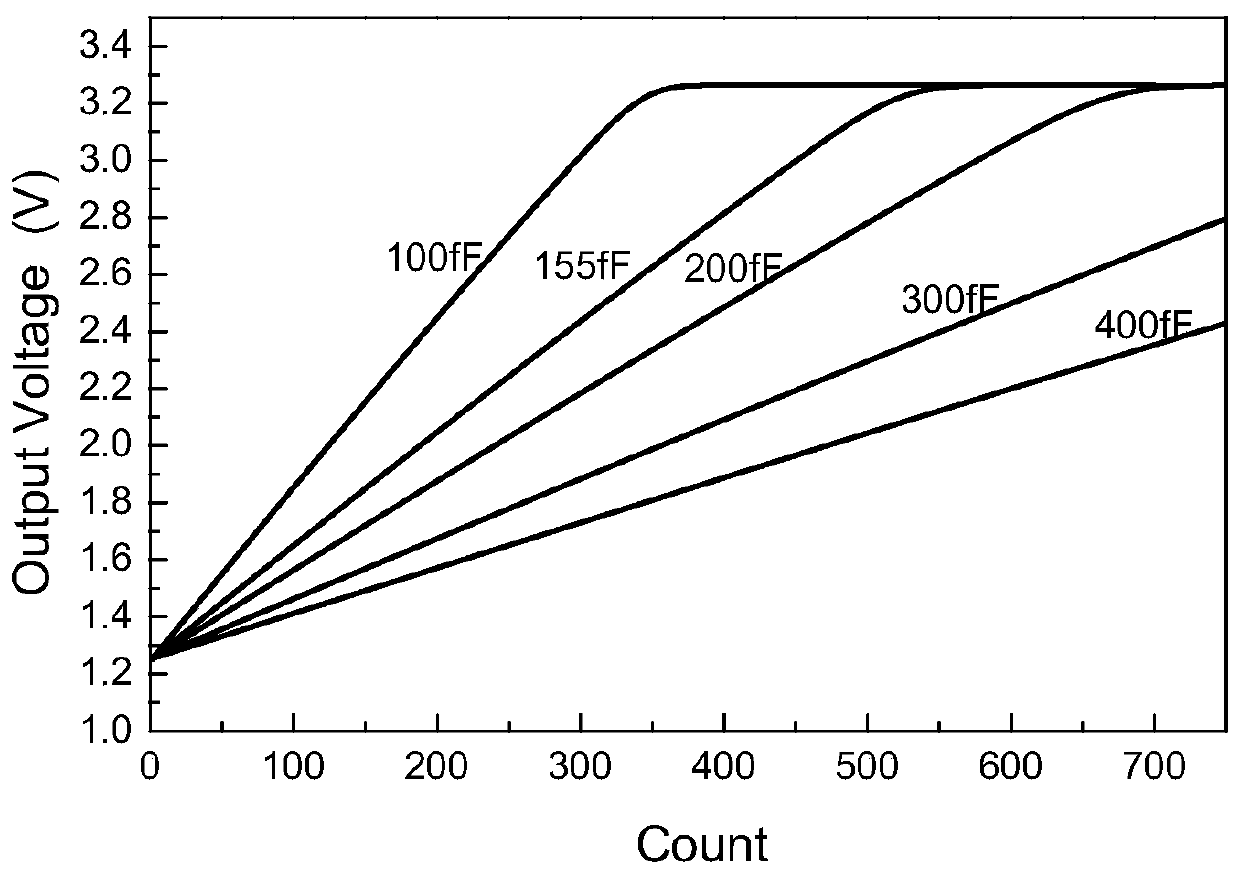

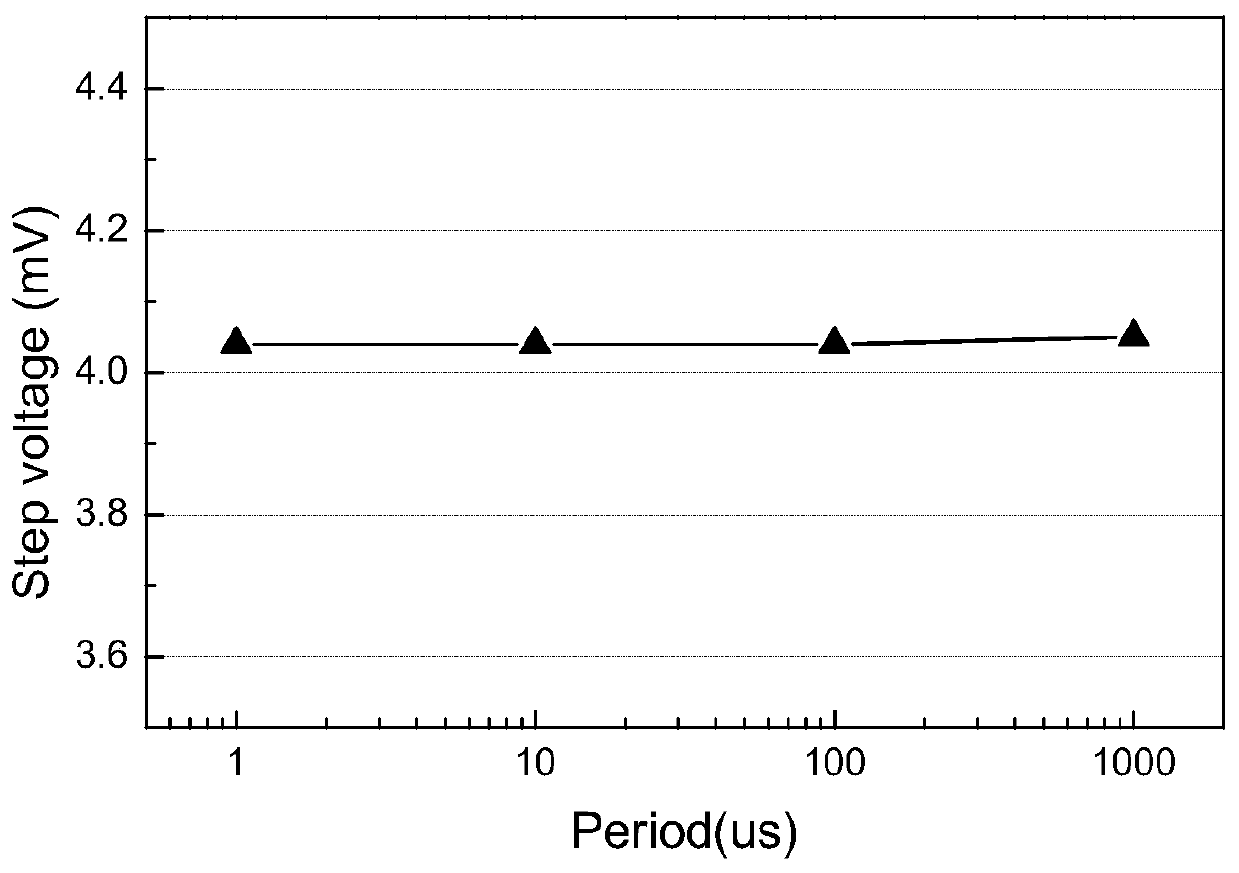

A technology of readout circuit and charge transfer, which is applied to the pulse counter of optoelectronic devices, the pulse counter of semiconductor devices with only two electrodes, pulse technology, etc., which can solve the problem of sensitive input avalanche pulse width and uniform counting step size Poor performance, poor counting step linearity and other problems, to achieve the effect of simple circuit, good performance consistency and high counting range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

[0023] Such as figure 1 As shown, the parameters of the MOSFET transistor and the integral capacitor in the analog counting readout circuit proposed by the present invention are set as follows: the length and the width of the input tube MP1 grid are 300nm; the length and the width of the charge transfer tube MP2 grid are respectively 2 μm and 300nm, the length and width of the gate of the source follower transistor MP3 are 300nm and 12μm respectively, and the length and width of the gate of the reset PMOS transistor MP4 are 300nm and 1μm respectively. Both MP5 and MP8 are used as current source loads, and the length and width of their gates are both 1 μm. MP6 and MP7 are used as unit gain amplifier input tubes, the length and width of the grid are 1 μm and 2 μm respectively, and the length and width of the grid of the row selection transistor MP9 are both 300 nm. The length and width of the gate of the reset NMOS transistor MN1 are 350nm and 440nm respectively, and the length...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com