A chip double-sided vertical packaging structure and packaging method

A packaging method and packaging structure technology, applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems of uneven upper and lower contact surfaces, large stress distribution of packaged products, and low online precision, etc., to achieve a good surface Flatness, adjustable packaging stress, compact size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

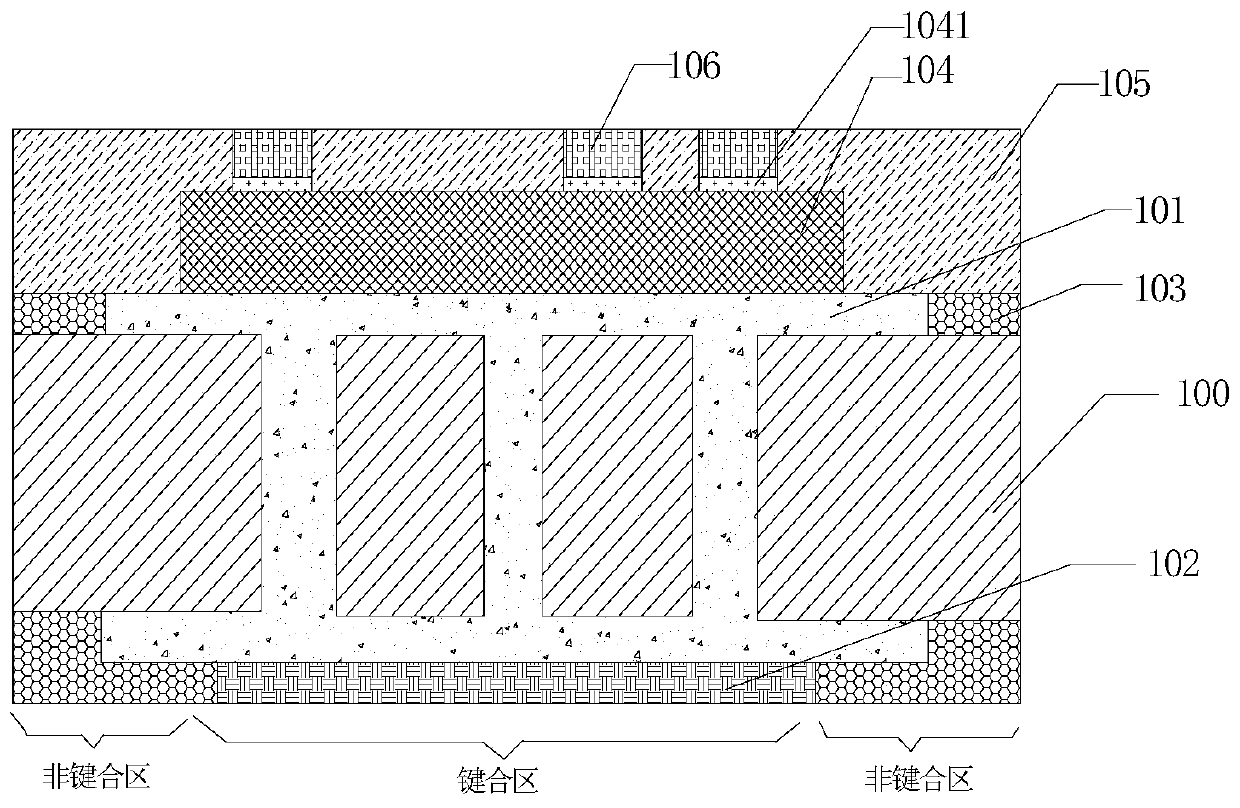

[0052] Such as figure 1As shown, this embodiment relates to a chip 104 double-sided vertical package structure, the package structure includes a PCB board 100, a conductive material layer 101, a first solder layer 102, a PCB solder resist layer 103, and a plurality of pads 1041 chip 104 are provided. , the plastic sealing layer 105 and the second solder layer 106; specifically, the above-mentioned PCB board 100 includes the PCB board 100 of the bonding area and the non-bonding area, and the PCB board 100 of the bonding area is provided with several conductive structures throughout; The material layer 101 includes a first conductive layer covering the upper surface of the PCB board 100 in the bonding area and a second conductive layer covering the lower surface of the PCB board 100 in the bonding area, and the first conductive layer and the second conductive layer pass through the above-mentioned several conductive layers. Structural electrical connection; the first solder laye...

Embodiment 2

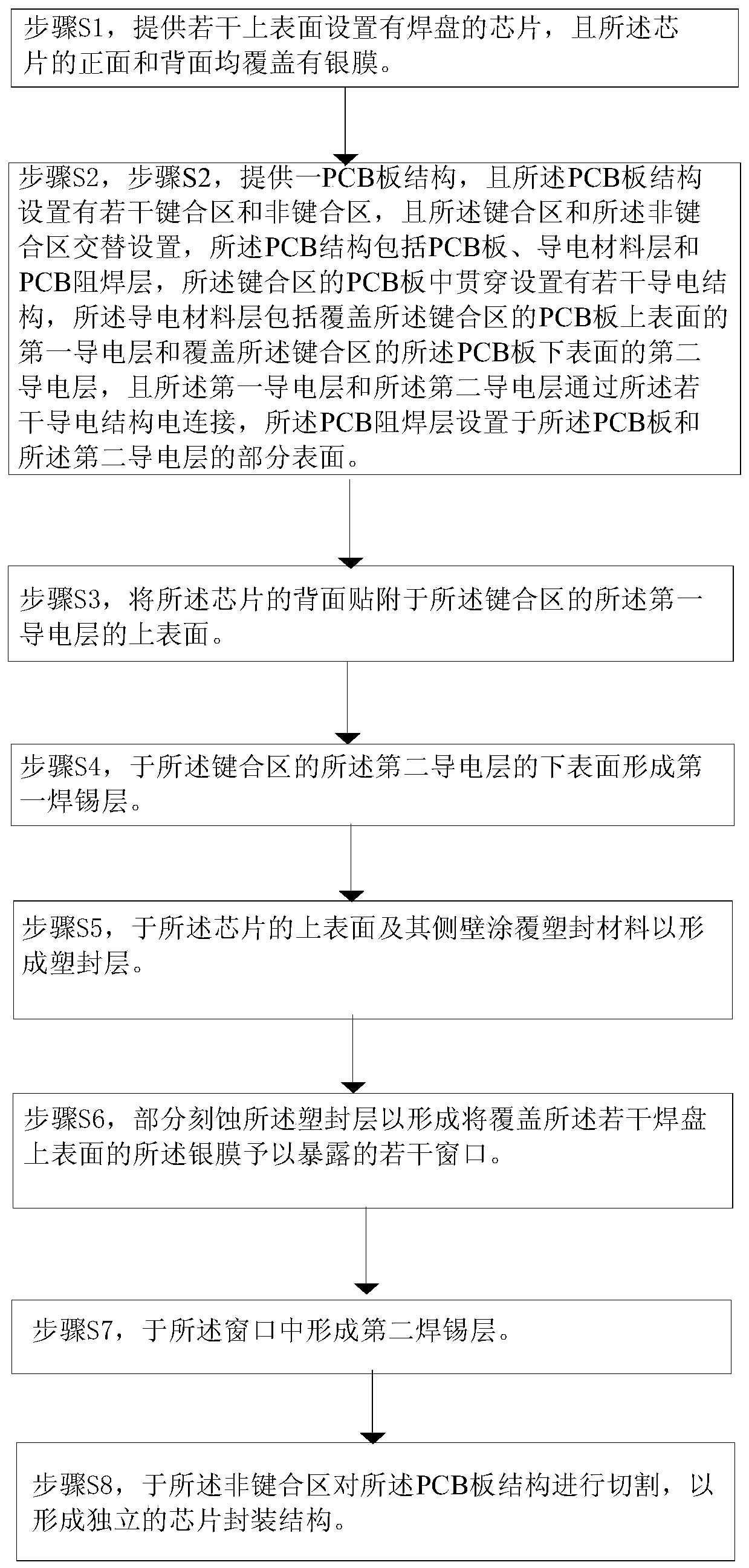

[0058] Such as figure 2 As shown, the present invention relates to a double-sided vertical packaging method for a chip 200. Specifically, the packaging method includes the following steps:

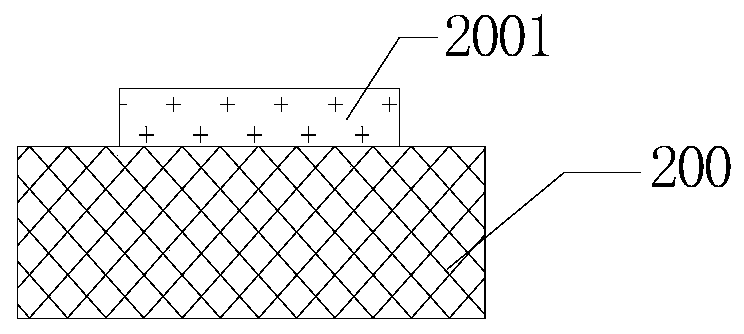

[0059] Step S1, provide several chips 200 with pads 2001 on the upper surface, and the front and back of the several chips 200 are covered with silver film (not shown in the figure), as image 3 structure shown.

[0060] In a preferred embodiment of the present invention, the chip 200 has a thickness of 30-500 μm (eg 30 μm, 200 μm, 265 μm or 500 μm).

[0061] In a preferred embodiment of the present invention, the thickness of the silver film is 1-9 μm (eg 1 μm, 3 μm, 5 μm or 9 μm, etc.).

[0062] In a preferred embodiment of the present invention, the above step S1 includes:

[0063] Step S11 , providing a wafer including a plurality of chips 200 , and each chip 200 is provided with a plurality of bonding pads 2001 (which may be one or more bonding pads 2001 ) on the upper surface.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com