Capacitance compensation and design method of gold wire bonding in a three-dimensional package circuit

A technology of capacitance compensation and three-dimensional packaging, which is applied to circuits, including printed capacitors, electrical components, etc., can solve the problems of occupying design space and limited improvement of microwave transmission performance, and achieve reduced area, compact structure, and low return loss. increased effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The embodiments of the present invention are described in detail below. This embodiment is implemented on the premise of the technical solution of the present invention, and detailed implementation methods and specific operating procedures are provided, but the protection scope of the present invention is not limited to the following implementation example.

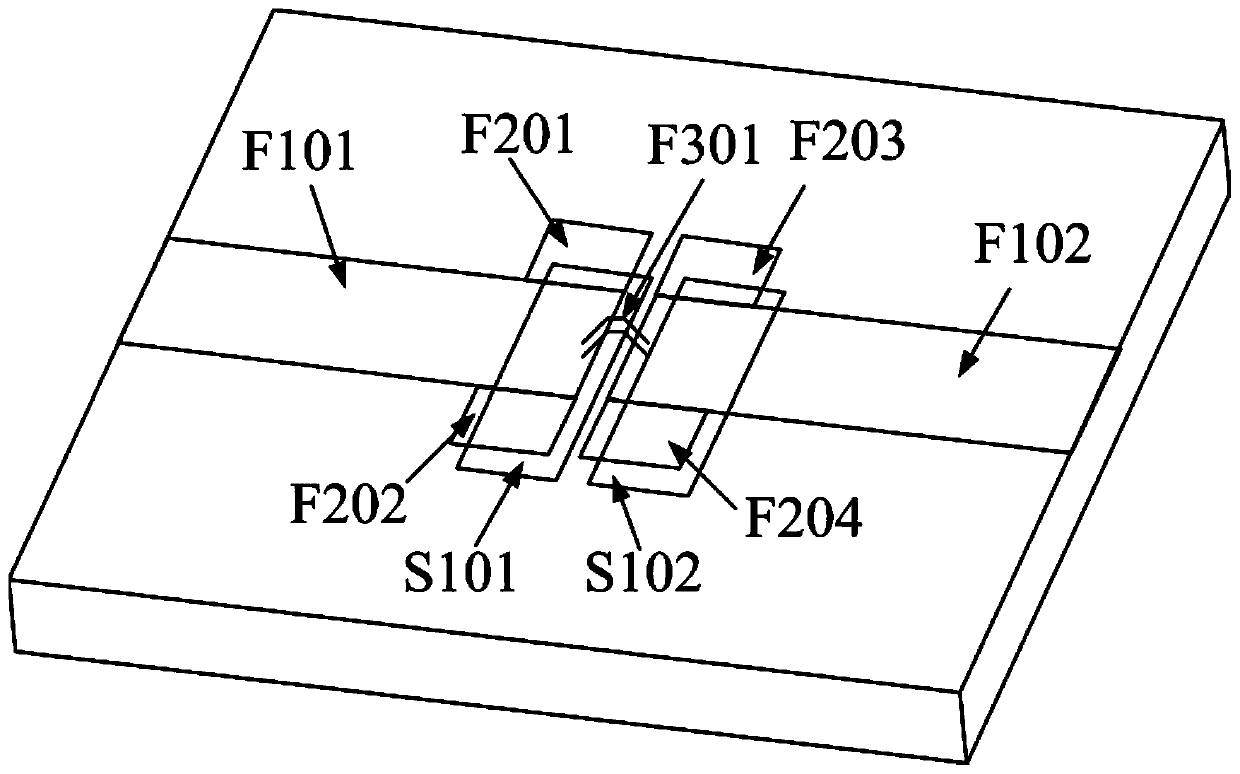

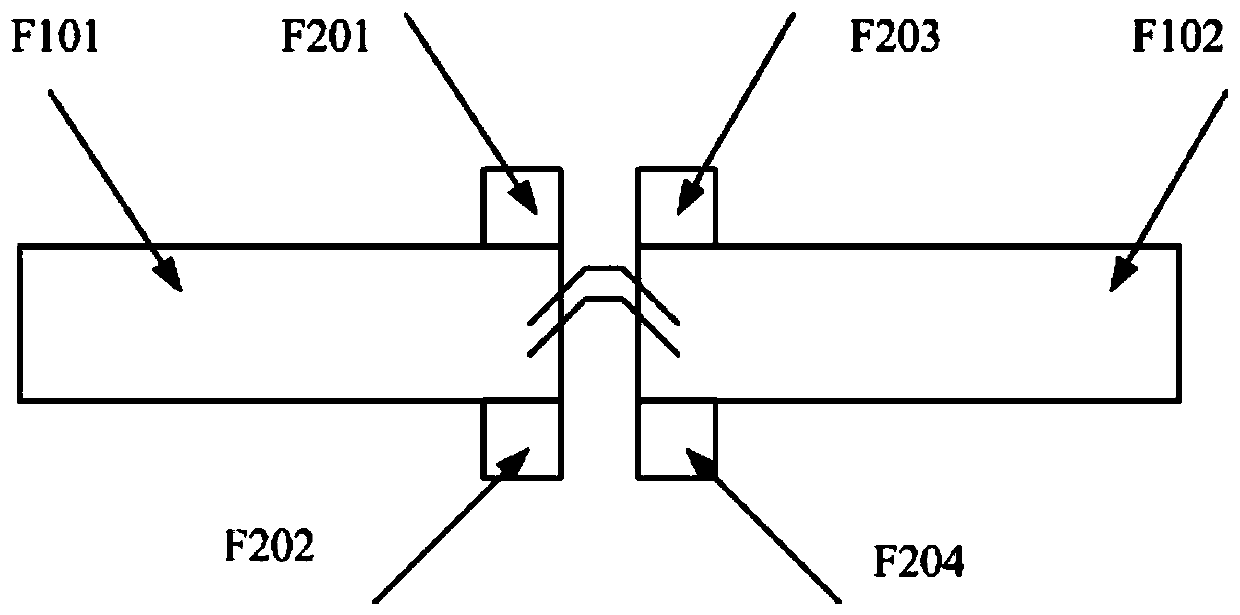

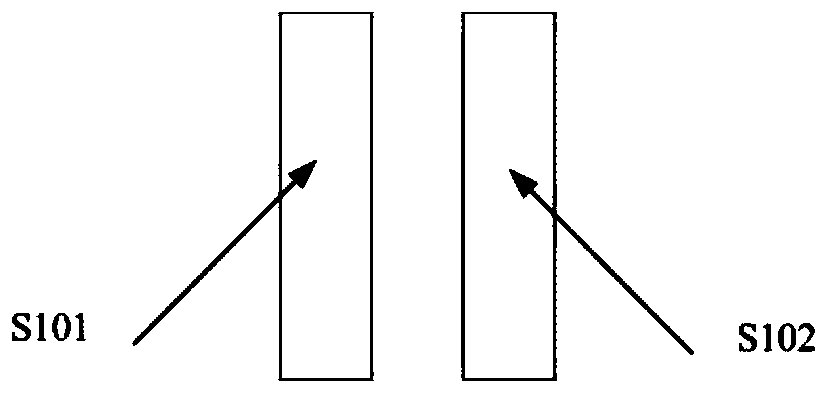

[0032] Such as figure 1 As shown, it is a three-dimensional diagram of the multilayer circuit gold wire bonding capacitance compensation design method according to the present invention, and the gold wire bonding F301 is connected between two 50-ohm first transmission lines F101 and second transmission lines F102. Wherein, the 50-ohm first transmission line F101 can be an input port or an output port, and correspondingly, the 50-ohm second transmission line F102 is an output port or an input port, and the two 50-ohm first transmission lines F101 and the second The transmission lines F102 are all in the form of 50 ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| dielectric loss | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com