A built-in self-test design method for multiple embedded memories on a single chip

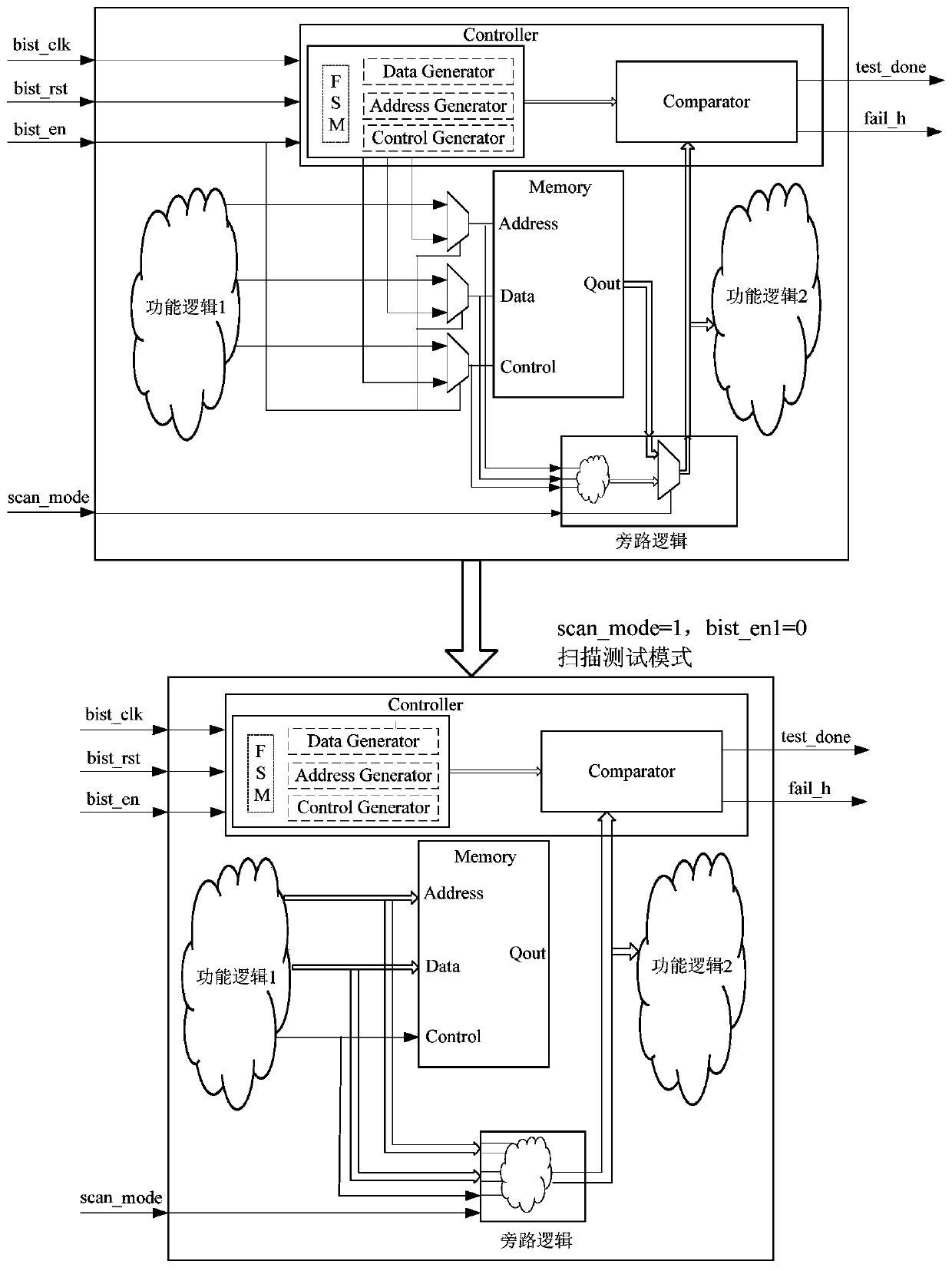

A technology of embedded memory and built-in self-test, which is applied in static memory, instruments, etc., can solve the problems of reduced scan test coverage, loss of scan test coverage, and excessively long windings, etc., to improve the overall scan test coverage , Conducive to timing convergence, reduce the effect of circuit power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0033] Take three memories Memory1, Memory2, and Memory3 on a single chip as an example, where Memory1 is a dual-port, the size is 2048 (that is, the address line width is 11 bits), the bit width is 8 bits, and the operating frequency is 120MHz. Both Memory2 and Memory3 are single ports, the size is 1024 (that is, the address line width is 10 bits), the bit width is 8 bits, and the working frequency is 60MHz. And in terms of layout, the distance between Memory2 and Memory3 is relatively close.

[0034] Using a batch tool, generate BIST libraries for the three memories. It is determined that Memory1 needs a controller Controller1, and Memory2 and Memory3 share a controller Controller2.

[0035] Add 2 memory test clock ports bist_clk1 and bist_clk2, memory test logic reset port bist_rst, 2 memory test enable ports bist_en1 and bist_en2, scan test mode port scan_mode, 2 memory test pass ports test_done1 and test_done2, 2 for a single chip Memory test fail ports fail_h1 and fail...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com