sio 2 medium charge and sio 2 Separation test method for /si interface state

A test method and interface state technology, applied in semiconductor/solid-state device testing/measurement, circuits, electrical components, etc., can solve the problems of unfavorable popularization and use of separation test methods, and achieve the advantages of popularization and use, low equipment requirements, and simple preparation process. quick effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

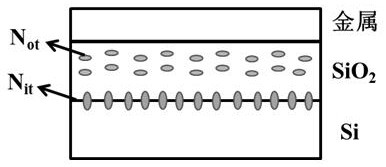

[0028] (1) Using the method of dry oxygen oxidation, grow 150 nm thick SiO on the surface of a p-type silicon wafer with a resistivity of 50 Ω.cm 2 thin film; subsequently, using the method of thermal evaporation on SiO 2 An aluminum thin film is grown on the surface, and then a MIS device is manufactured. The structure diagram of the corresponding MIS device and where N o t and N it distribution, such as figure 1 shown.

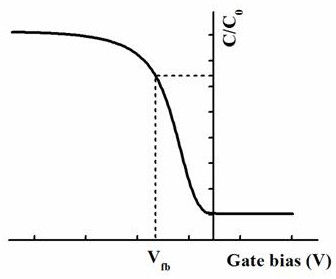

[0029] (2) At normal temperature, carry out C / V test to the MIS device described in step (1), the corresponding C / V curve is as follows figure 1 shown. Obtain the flat band voltage V from the C / V curve fb , and then calculate the total charge density N tot (N tot =N ot + N it ). The corresponding C / V curve is as figure 2 Shown:

[0030] N tot = (W ms -V fb ).C ox (1)

[0031] Among them, N tot is the total charge concentration, N tot =N ot + N it ;W ms is the difference between the metal and semiconductor work functions, and the ...

Embodiment 2

[0038] (1) Using the plasma-enhanced chemical vapor deposition method, a 30 nm thick SiO was grown on the surface of an n-type silicon wafer with a resistivity of 0.1 Ω.cm 2 thin film; subsequently, using the method of magnetron sputtering on SiO 2 A gold film is grown on the surface, and then the MIS device is made;

[0039] (2) At normal temperature, carry out C / V test to the MIS device described in step (1), obtain flat-band voltage V fb , and then calculate the total charge density N tot (N tot =N ot + N it );

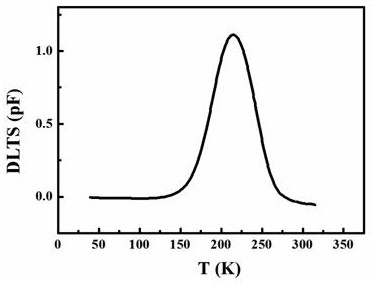

[0040] (3) Further, the deep-level transient spectroscopy (DLTS) test is carried out on the MIS device described in step (1), and the test temperature range is 20-300K. According to the measured deep-level transient spectrum curve, combined with formula (2), the distribution of the energy level density of the interface state with the energy level is calculated, and the energy level density of the interface state is integrated with the energy level to obtain...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com