A method to introduce solid impurities to the silicon material in the room temperature environment

A silicon material, solid-state technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as polluting the environment, high cost, and contamination of silicon materials

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

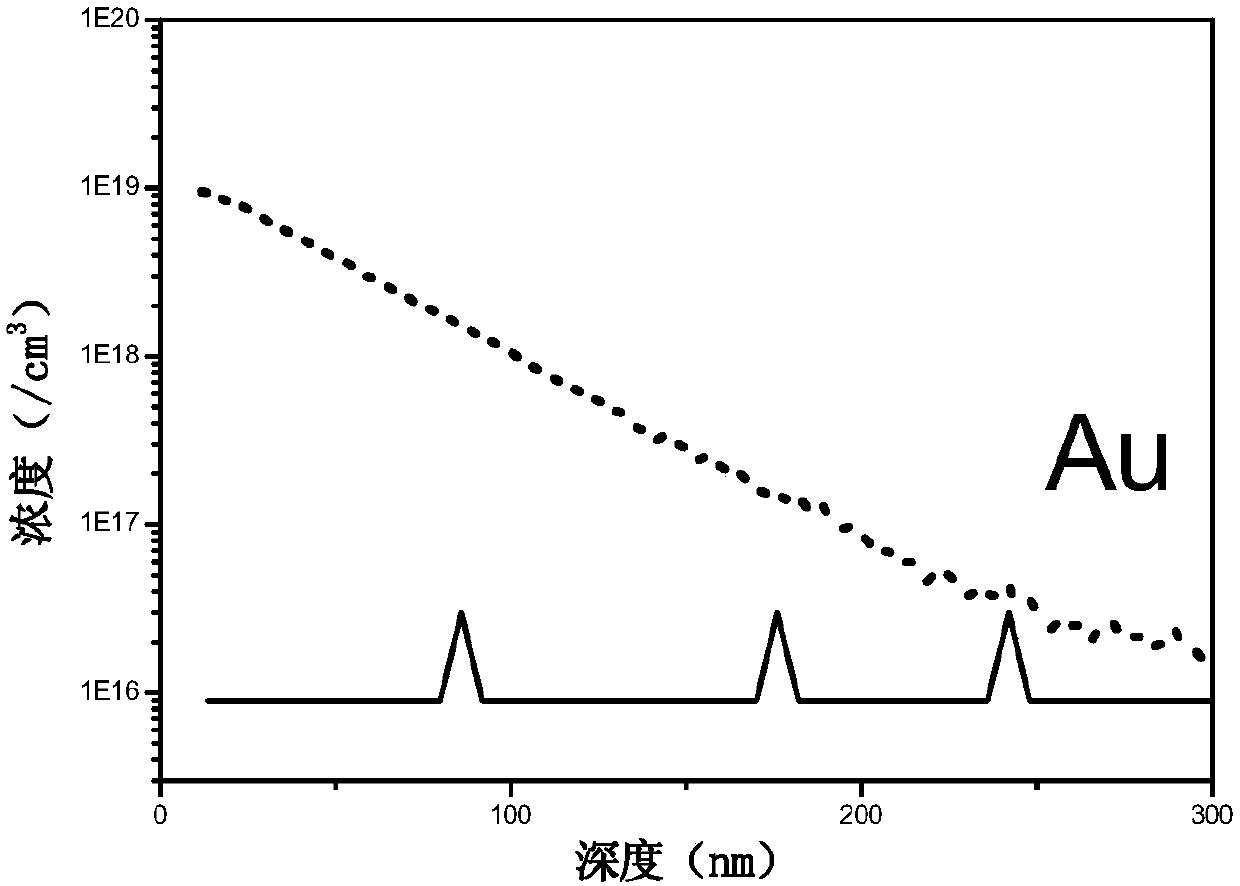

[0026] A P-type solar-grade Czochralski silicon single wafer is selected, polished on one side, with a resistivity of 1.9Ω·cm and a thickness of 625μm. Firstly, silicon wafers were ultrasonically cleaned with acetone, ethanol, and deionized water for 10 min, and then immersed in 2% HF solution to remove the natural oxide layer on the surface of the silicon wafers. Then the gold foil is placed in the center of the bottom of the plasma reaction chamber, the silicon wafer faces the gold foil, and is placed in an area at a certain distance from the center of the bottom of the plasma reaction chamber. The working gas is helium, the flow rate is 22sccm, and the vacuum degree is about 5E-3Pa. The power of the excitation power supply is 750W, and the processing time is 2min. Finally, the SIMS method was used to obtain the distribution of Au impurity concentration with depth in the sample after plasma treatment. The results are as follows: figure 1 shown. After 750W plasma treatment...

Embodiment 2

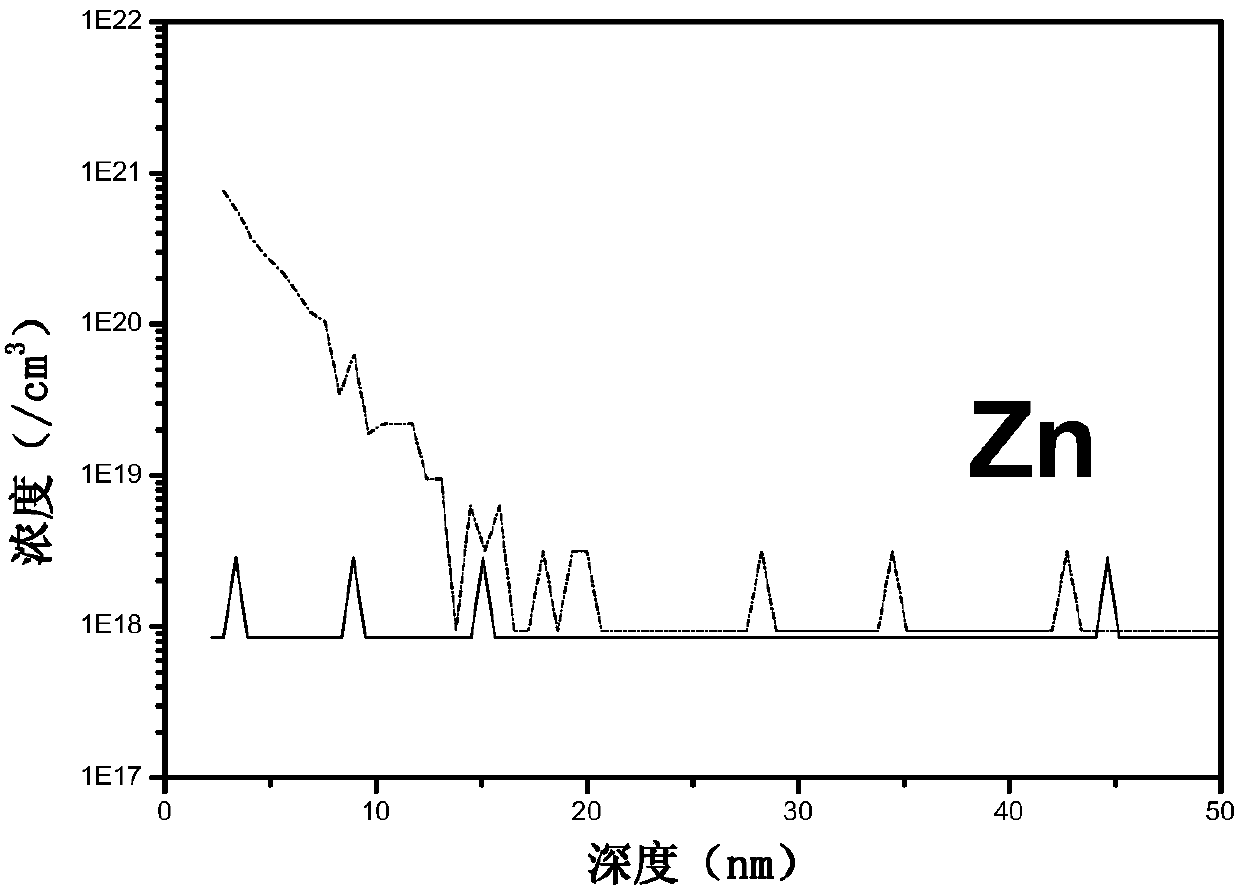

[0028] A P-type solar-grade Czochralski silicon single wafer is selected, polished on one side, with a resistivity of 1.9Ω·cm and a thickness of 625μm. Firstly, silicon wafers were ultrasonically cleaned with acetone, ethanol, and deionized water for 10 min, and then immersed in 2% HF solution to remove the natural oxide layer on the surface of the silicon wafers. Next, the zinc ingot is placed in the center of the bottom of the plasma reaction chamber, and the silicon sheet faces the zinc ingot, and is placed in an area at a certain distance from the center of the bottom of the plasma reaction chamber. The working gas is helium, the flow rate is 22sccm, and the vacuum degree is about 5E-3Pa. The power of the excitation power supply is 750W, and the processing time is 2min. Finally, the SIMS method was used to obtain the distribution of Zn impurity concentration with depth in the sample after plasma treatment. The results are as follows: figure 2 shown. After 750W plasma t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com