FPGA circuit transmission delay rest system and method based on TDC

A transmission delay and testing system technology, applied in electronic circuit testing, measuring electricity, measuring devices, etc., can solve the problems of strong professional and technical requirements of testers, difficulty in testing internal modules of chips, and high testing costs, reducing equipment and manpower. Low cost, low test equipment requirements, good versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

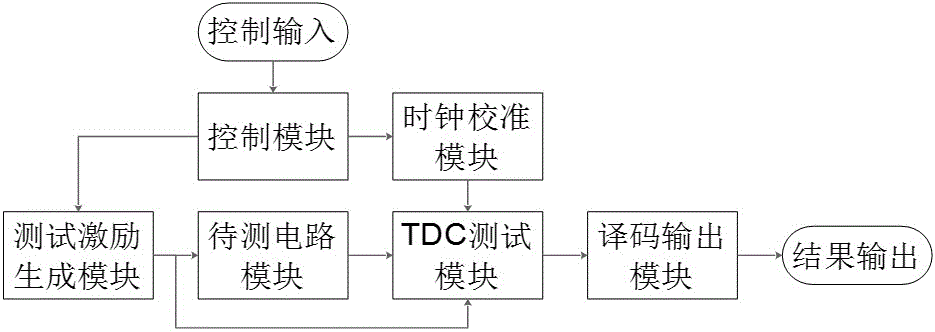

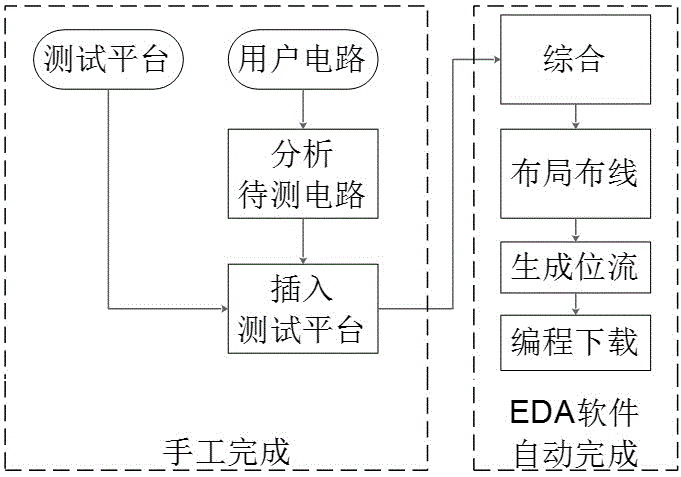

[0019] The basic implementation process of the system of the present invention is as follows: figure 2 shown.

[0020] Among them, the EDA tool generally chooses the EDA tool provided by the FPGA chip manufacturer itself, such as the ISE series software of Xilinx Company, or the Quartus series software of Altera Company. The test platform is generally described in the form of industry-standard HDL code, and an appropriate TDC structure is selected according to the characteristics of the FPGA to be tested. The circuit to be tested can flexibly choose methods such as hard macro (hard macro), IP core, HDL code description according to the test requirements, as long as it can accept EDA tool synthesis.

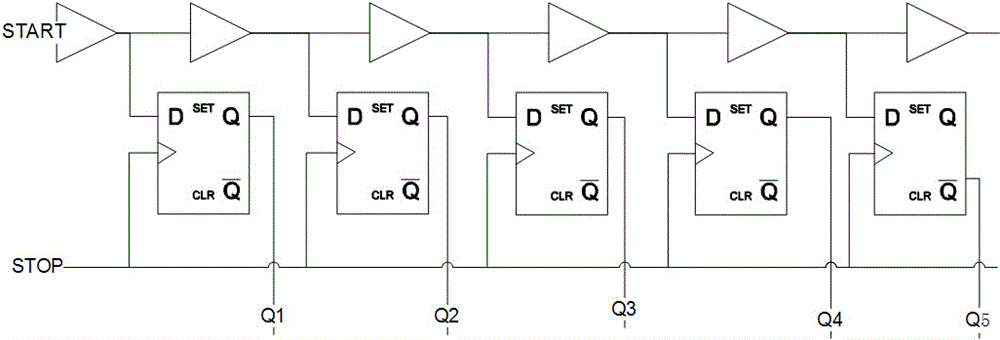

[0021] Taking a test process based on ISE EDA software as an example, the TDC test platform is described in the form of HDL language, and the circuit to be tested is described in the form of hard macros to avoid comprehensive interference. Before starting the test, first creat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com