High-energy-efficiency low-jitter single loop clock data recovery circuit

A clock data recovery, low jitter technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of increasing power consumption and design complexity, phase deviation, affecting the jitter performance of the clock data recovery circuit, and improving the jitter performance. , the effect of reducing area burden and design complexity, reducing the number of polyphase clocks and overall power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

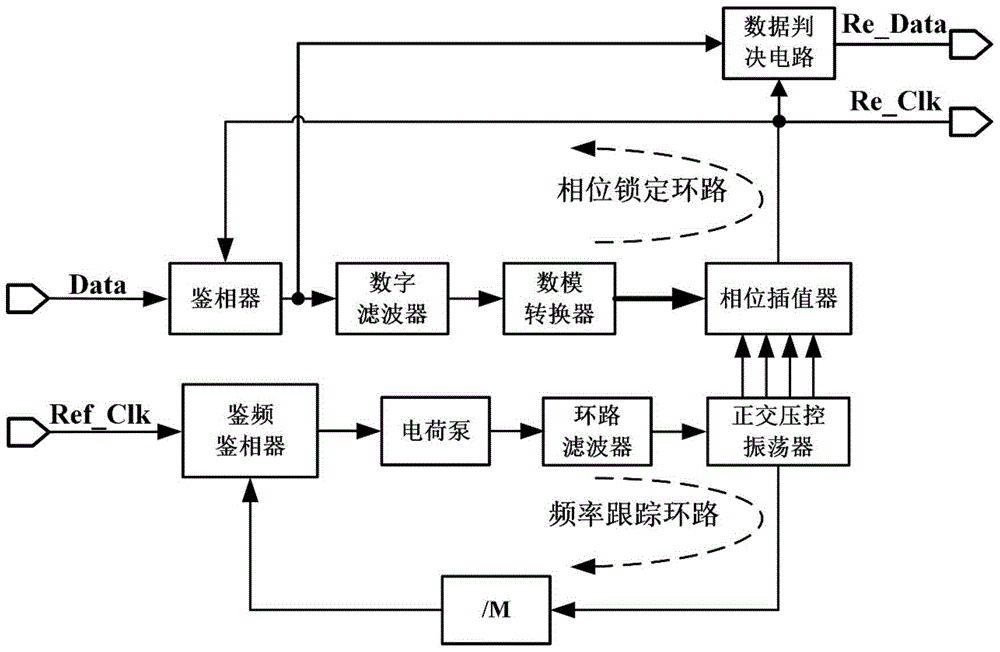

[0031] refer to Figure 4 , a high-energy-efficiency and low-jitter single-loop clock data recovery circuit proposed by the present invention includes: a phase detector, a voltage-current converter, a loop filter and a multi-phase clock generator. Wherein, the phase detector adopts a 1 / N rate Bang-Bang phase detector, which includes a 1:N splitter functional module.

[0032] The first input terminal of the phase detector is connected to the input data DATA, its output terminal is connected to the voltage-current converter, the output terminal of the voltage-current converter is connected to the input terminal of the loop filter, and the output terminal of the loop filter is connected to the multiple The input end of the phase clock generator is connected, and the output end of the multi-phase clock generator is connected with the second input end of the phase detector.

[0033] The phase detector receives the input data and the M-phase clock signal output by the multi-phase c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com