A super junction mosfet

A gate structure and substrate technology, applied in semiconductor devices, electrical components, circuits, etc., to improve the ability to resist UIS failures, suppress parasitic transistors from turning on, and improve reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

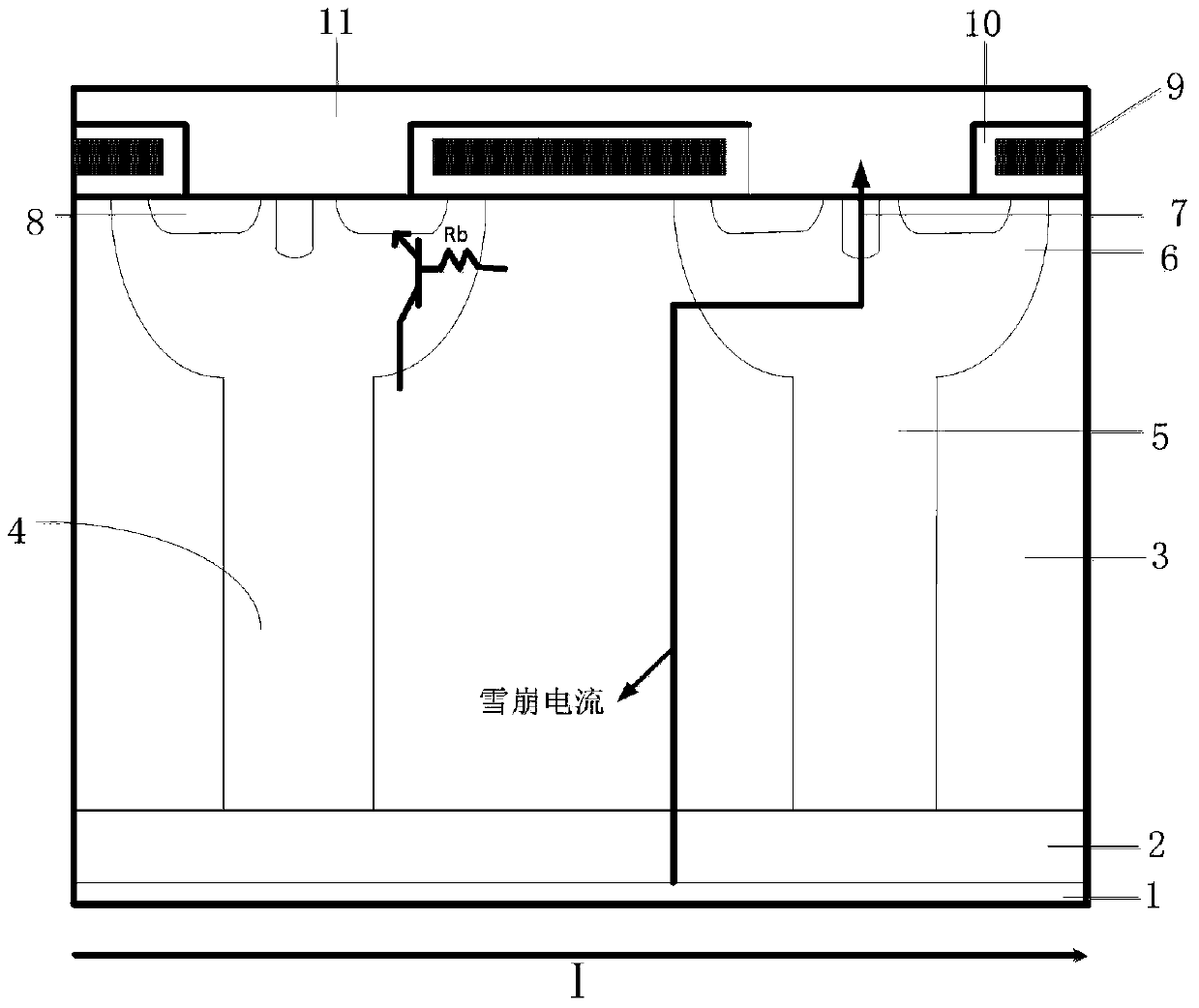

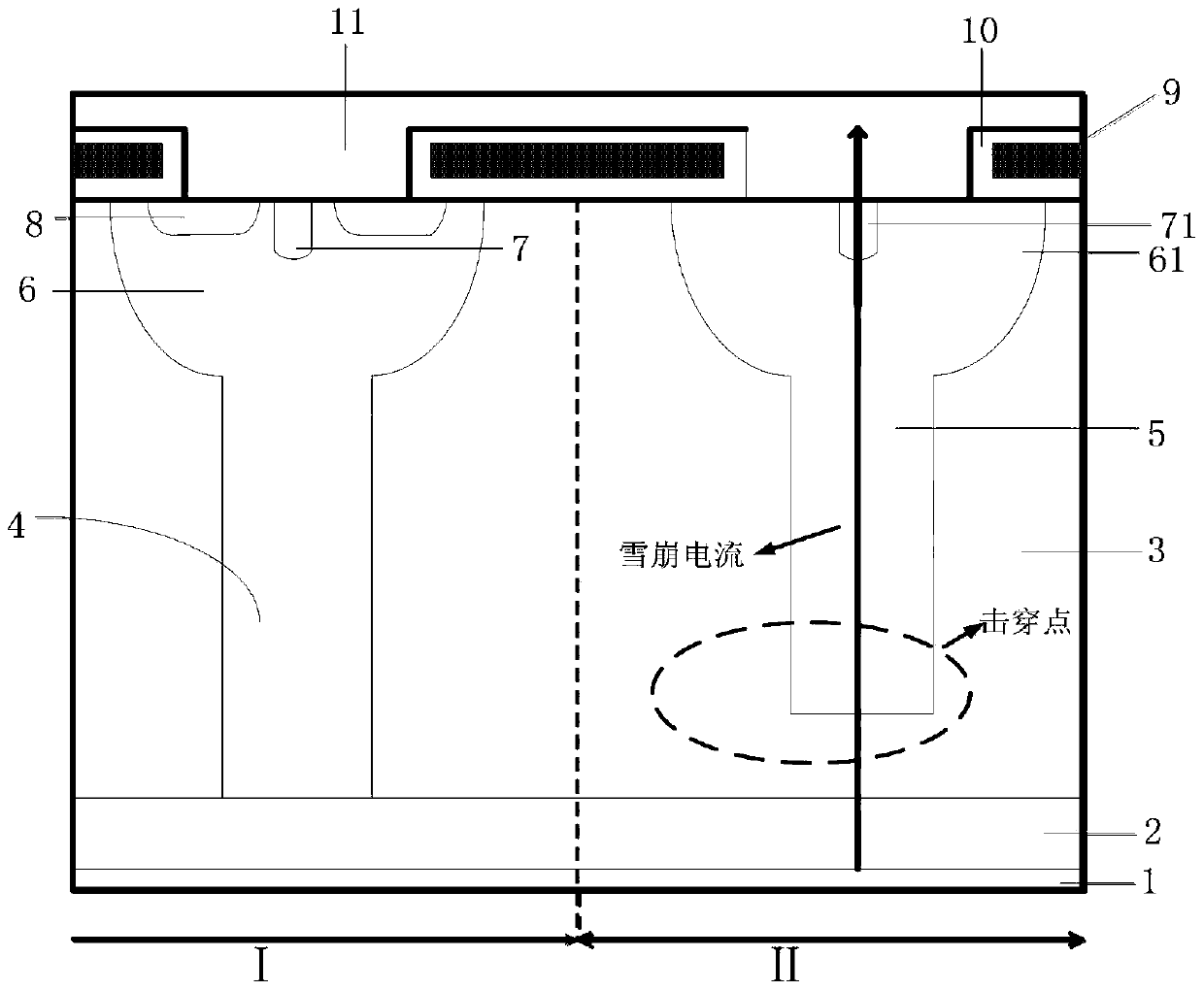

[0026] Such as figure 2 As shown, this example includes normal cell area I (only one cell is shown in the figure) and pseudo cell II; the normal cell area I and pseudo cell II share the same metal drain electrode 1, metal drain electrode 1 Above is the N+ substrate 2, and above the N+ substrate 2 is the N epitaxial region 3; the N epitaxial region 3 has the first P-type column 4 in the normal cell and the second P-type column 5 in the dummy cell ; The first P-type column 4 and the N epitaxial layer 3 of the normal cell meet the charge balance, the top of the first P-type column 4 is the first P-type body region 6, and the N+ active region 8 is located inside the first P-type body region 6 And connected to the source electrode 11, there is a P+ contact region 7 also connected to the source electrode 11 between the N+ active regions 8; the second P-type column 5 of the pseudo-cell is the same as the doping concentration of the first P-type column 4 and the second P-type column ...

Embodiment 2

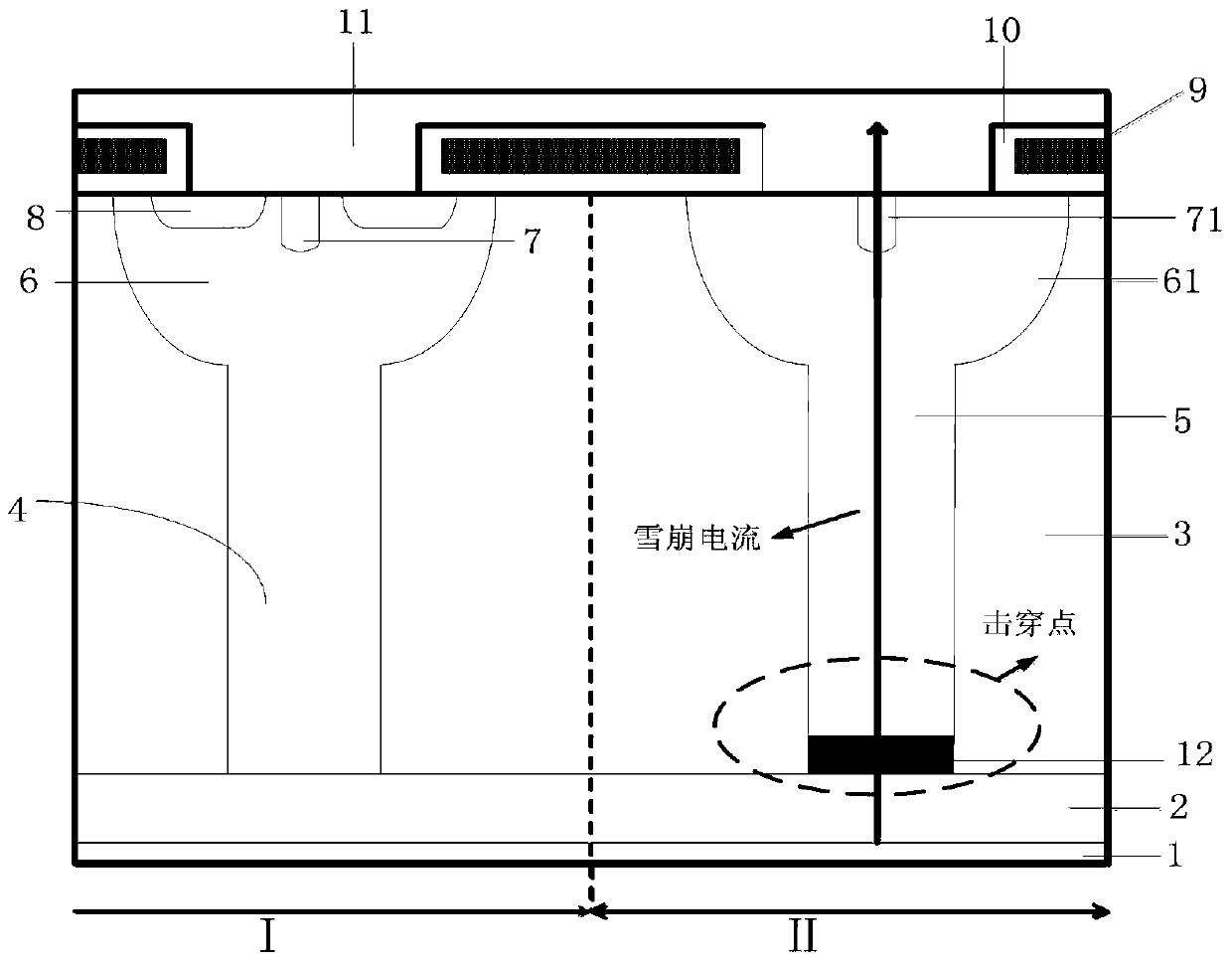

[0028] Such as image 3As shown, this example includes normal cell area I (only one cell is shown in the figure) and pseudo cell II; the normal cell area I and pseudo cell II share the same metal drain electrode 1, metal drain electrode 1 Above is the N+ substrate 2, and above the N+ substrate 2 is the N epitaxial region 3; the N epitaxial region 3 has the first P-type column 4 in the normal cell and the second P-type column 5 in the dummy cell ; The first P-type column 4 and the N epitaxial layer 3 of the normal cell meet the charge balance, the top of the first P-type column 4 is the first P-type body region 6, and the N+ active region 8 is located inside the first P-type body region 6 And connected to the source electrode 11, there is a P+ contact region 7 also connected to the source electrode 11 between the N+ active regions 8; the second P-type column 5 of the pseudo-cell is the same as the doping concentration of the first P-type column 4 and the second P-type column 4 ...

Embodiment 3

[0030] Such as Figure 4 As shown, this example includes normal cell area I (only one cell is shown in the figure) and pseudo cell II; the normal cell area I and pseudo cell II share the same metal drain electrode 1, metal drain electrode 1 Above the N+ substrate 2, on the N+ substrate 2 is the N epitaxial region 3; the N epitaxial region 3 includes the first P-type column 4 in the normal cell and the second P-type column 5 in the dummy cell ; The first P-type column 4 and the N epitaxial layer 3 of the normal cell meet the charge balance, the top of the first P-type column 4 is the first P-type body region 6, and the N+ active region 8 is located inside the first P-type body region 6 And connected to the source electrode 11, there is a P+ contact region 7 also connected to the source electrode 11 between the N+ active regions 8; the second P-type column 5 of the pseudo-cell is the same depth as the first P-type column 4 and the second P The overall concentration of the pilla...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com