Calculation method of chip surface contact pressure and variable-scale manufacturability design method

A technology of contact pressure and calculation method, applied in the direction of calculation, instrument, electrical and digital data processing, etc., can solve the problem of lack of CMP model realization technology, and achieve the effect of optimizing the design method for manufacturability and improving the calculation accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

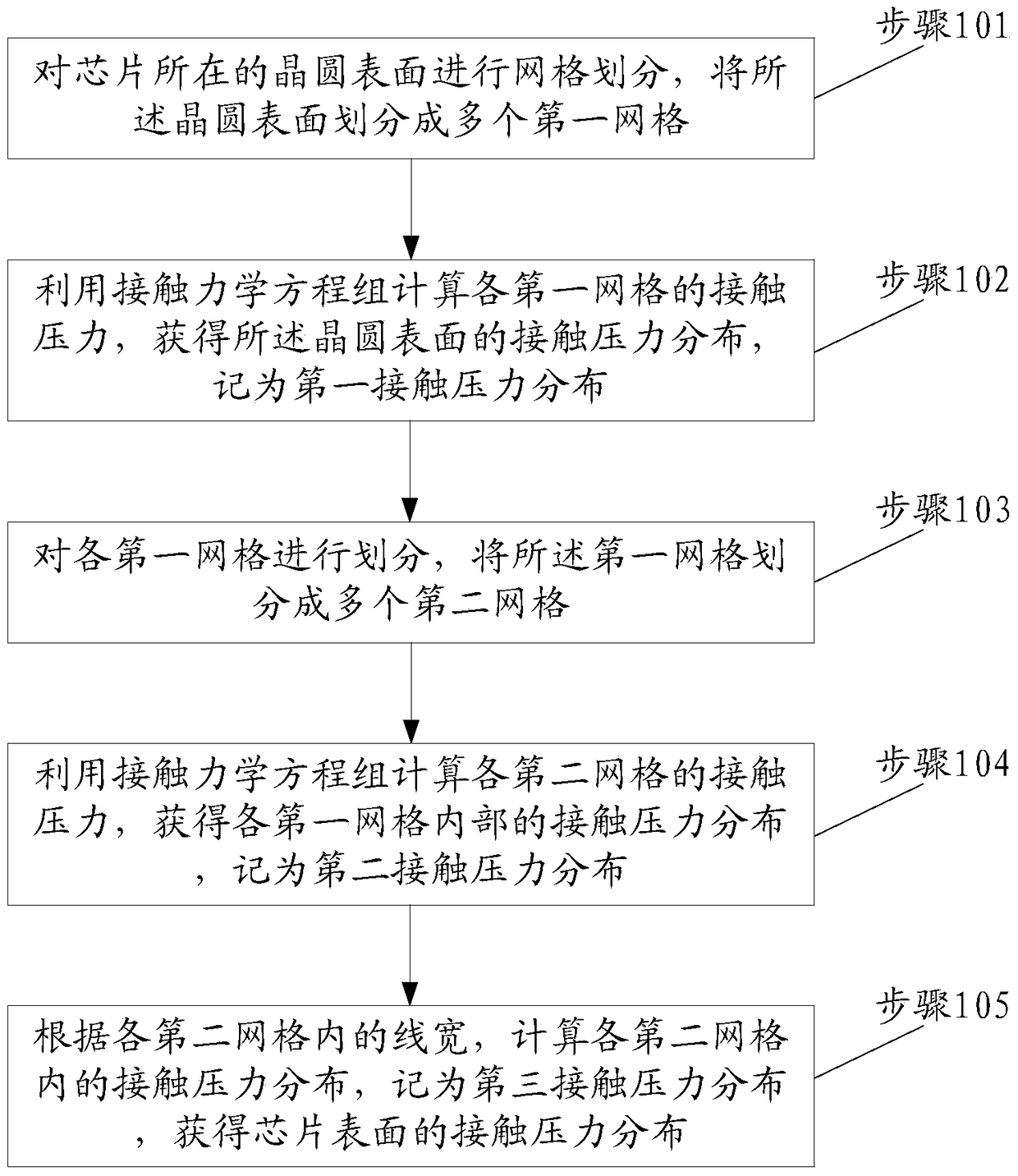

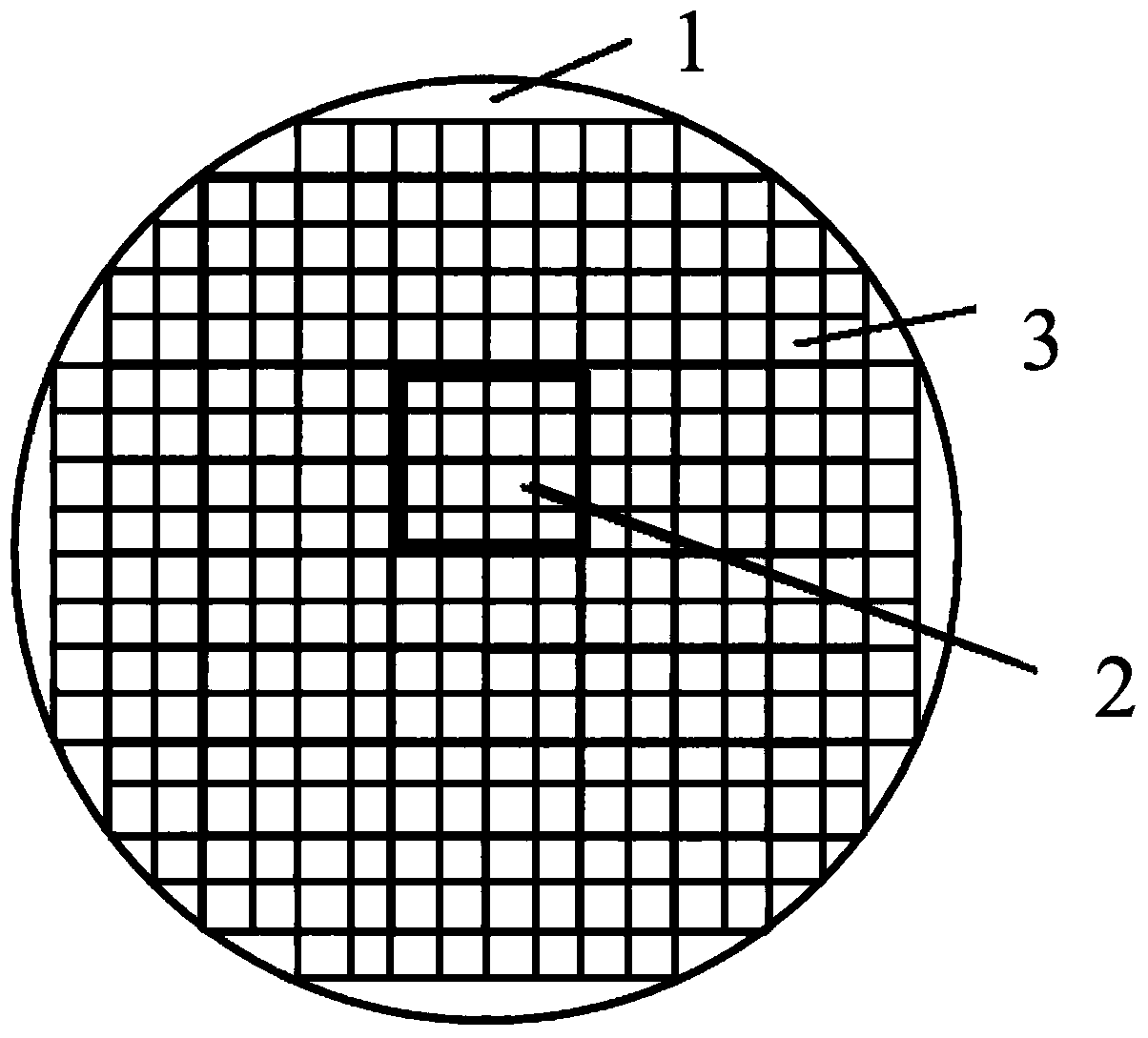

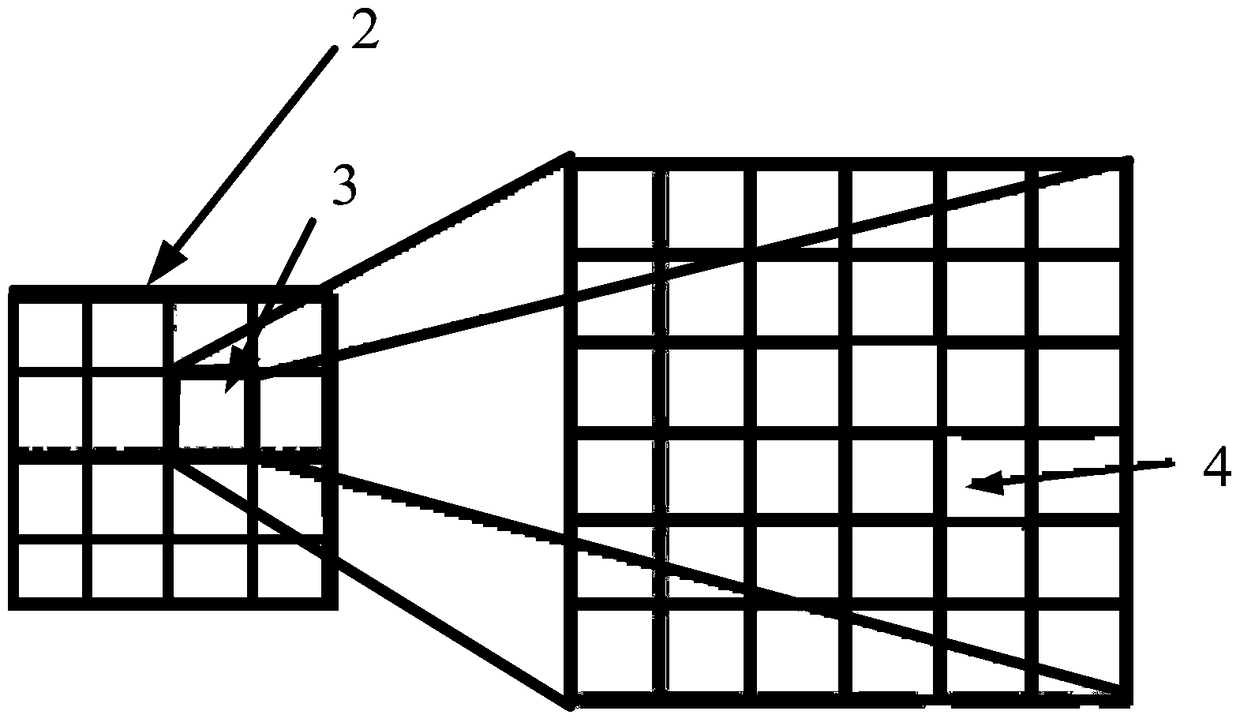

Method used

Image

Examples

Embodiment Construction

[0059] As mentioned in the background technology section, in the prior art, the CMP model and implementation technology that can take into account both the grinding mechanism and the calculation efficiency of the contact pressure between the polishing pad and the surface of the chip are very scarce, resulting in a polishing pad and chip that can take into account both calculation efficiency and accuracy. The research on the calculation method of contact pressure between surfaces has become an important topic in the process of CMP dynamic simulation.

[0060] The inventor found that in recent years, CMP theory and simulation research have promoted the application of CMP models in process simulation and design optimization, but there are not many chip-level CMP models that are actually adopted by design companies and developed into products. The geometric semi-empirical models of Provincial Institute of Technology and Berkeley are the main ones. This is mainly because there are ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com