Synchronous buck DC-DC converter capable of achieving low output ripples in times of underloading

A DC-DC converter technology, applied in the field of synchronous step-down DC-DC converters, can solve the problems of excessive output ripple, large time constant, large output ripple at the output end, etc., to achieve output ripple The effect of reducing and improving light-load efficiency and expanding the scope of application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

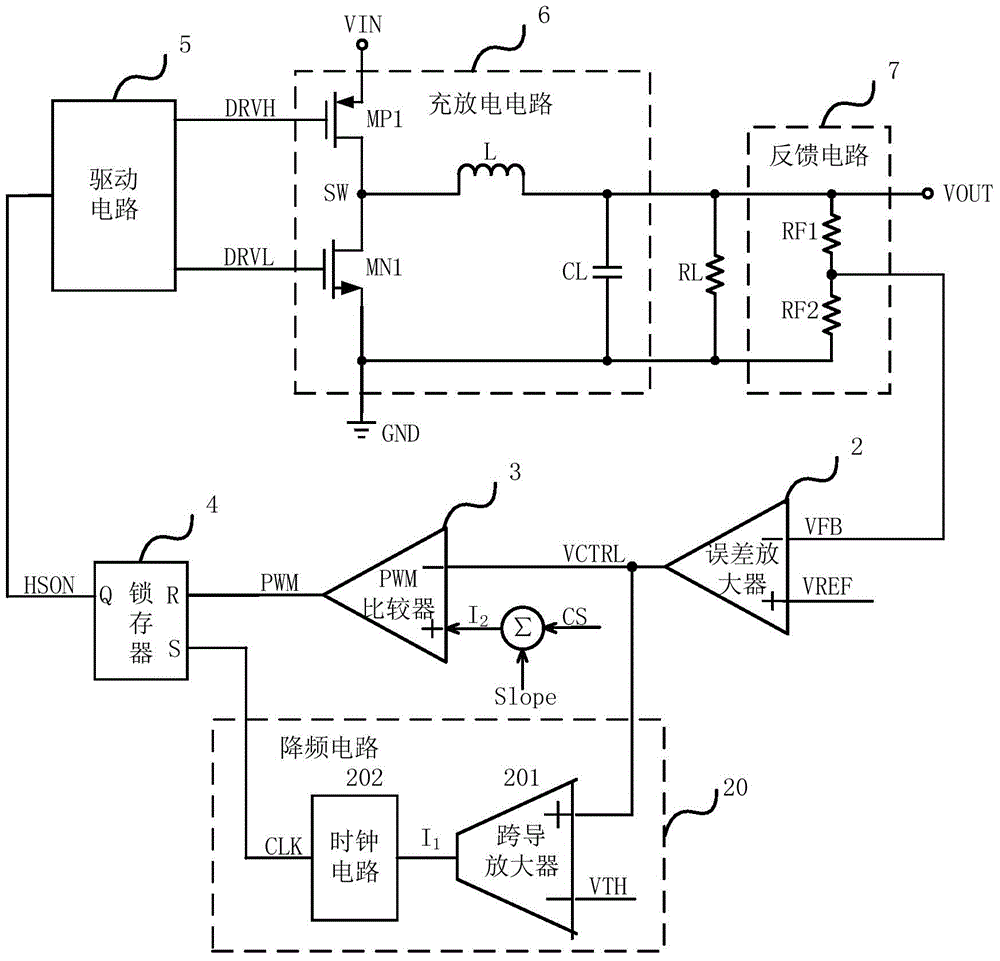

[0053] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

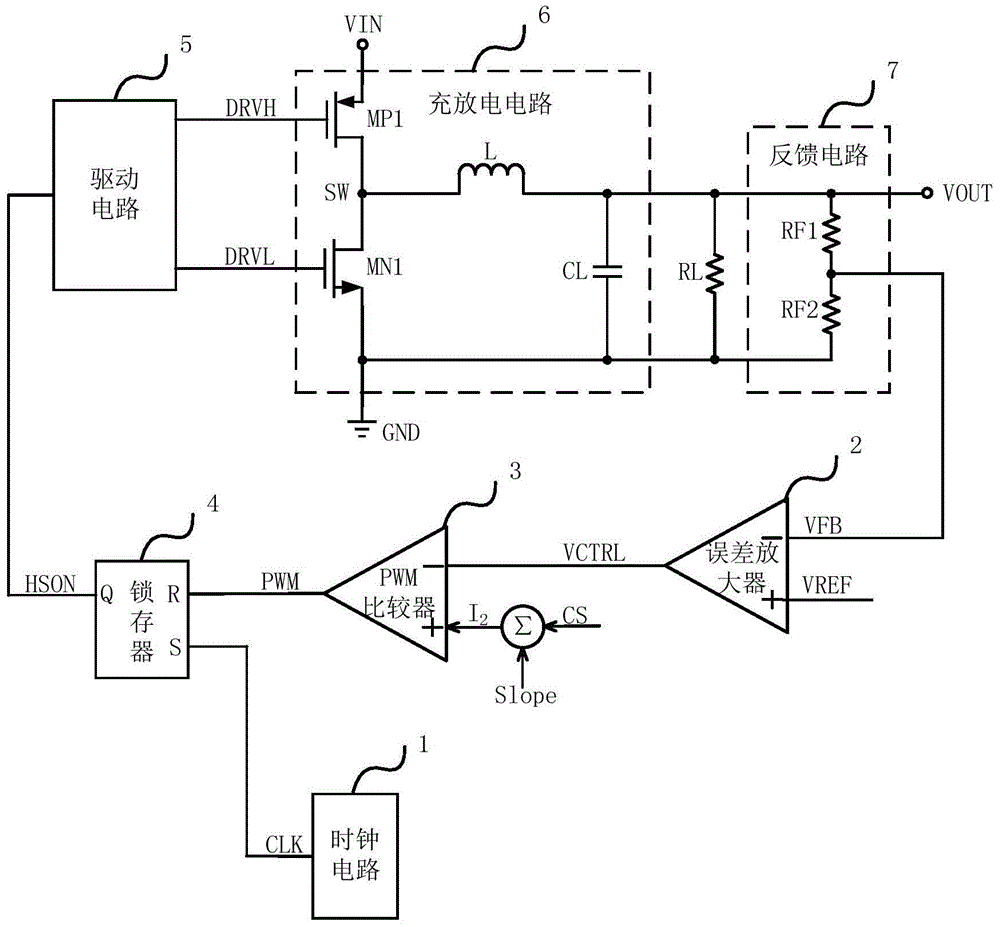

[0054] figure 1 shows a block diagram of a prior art synchronous step-down DC-DC converter, such as figure 1 As shown, prior art synchronous step-down DC-DC converters include:

[0055] A clock circuit 1, the output terminal of the clock circuit 1 is connected to the setting terminal S of the latch 4;

[0056] Error amplifier 2, the positive phase input terminal of the error amplifier 2 inputs the reference voltage signal VREF, the negative phase input terminal of the error amplifier 2 is connected to the output terminal of the feedback circuit, and the output terminal of the error amplifier 2 is connected to the negative phase input terminal of the PWM comparator ;

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com