Power semiconductor device and manufacturing method thereof

A technology of power semiconductors and devices, which is applied in the manufacture of power semiconductor devices and the field of power semiconductor devices, and can solve problems such as long manufacturing cycle, hard reverse recovery characteristics of diodes, and severe fluctuations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

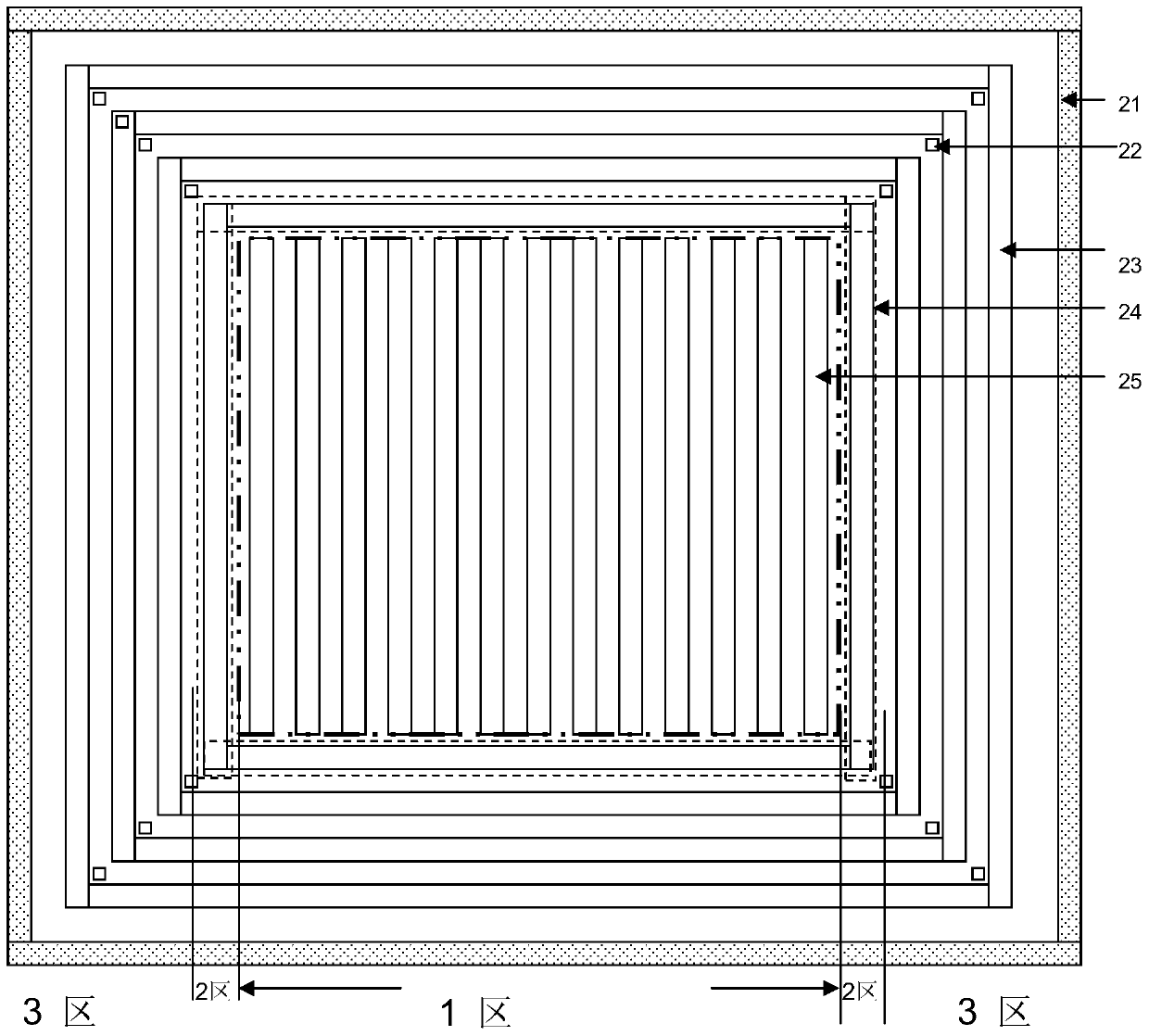

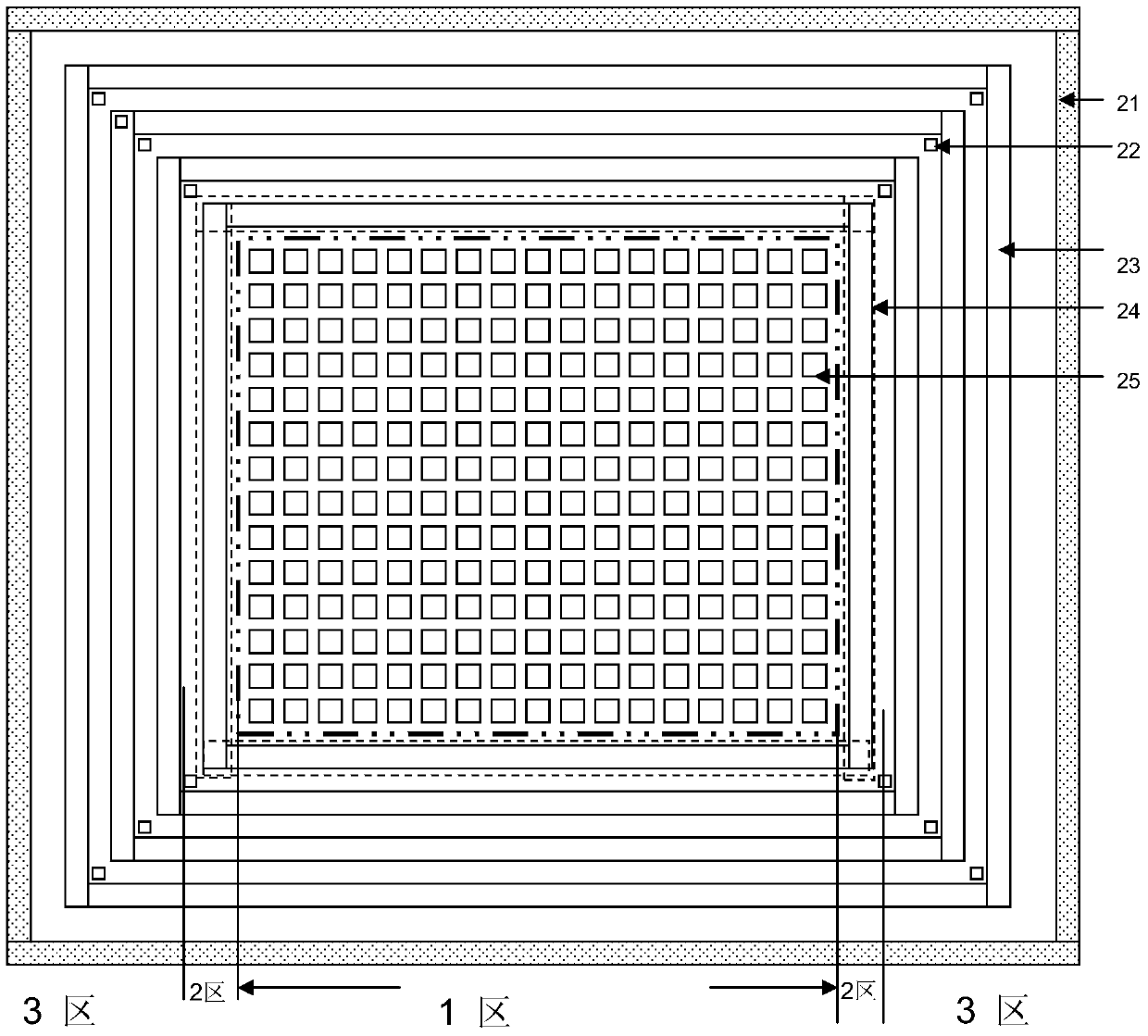

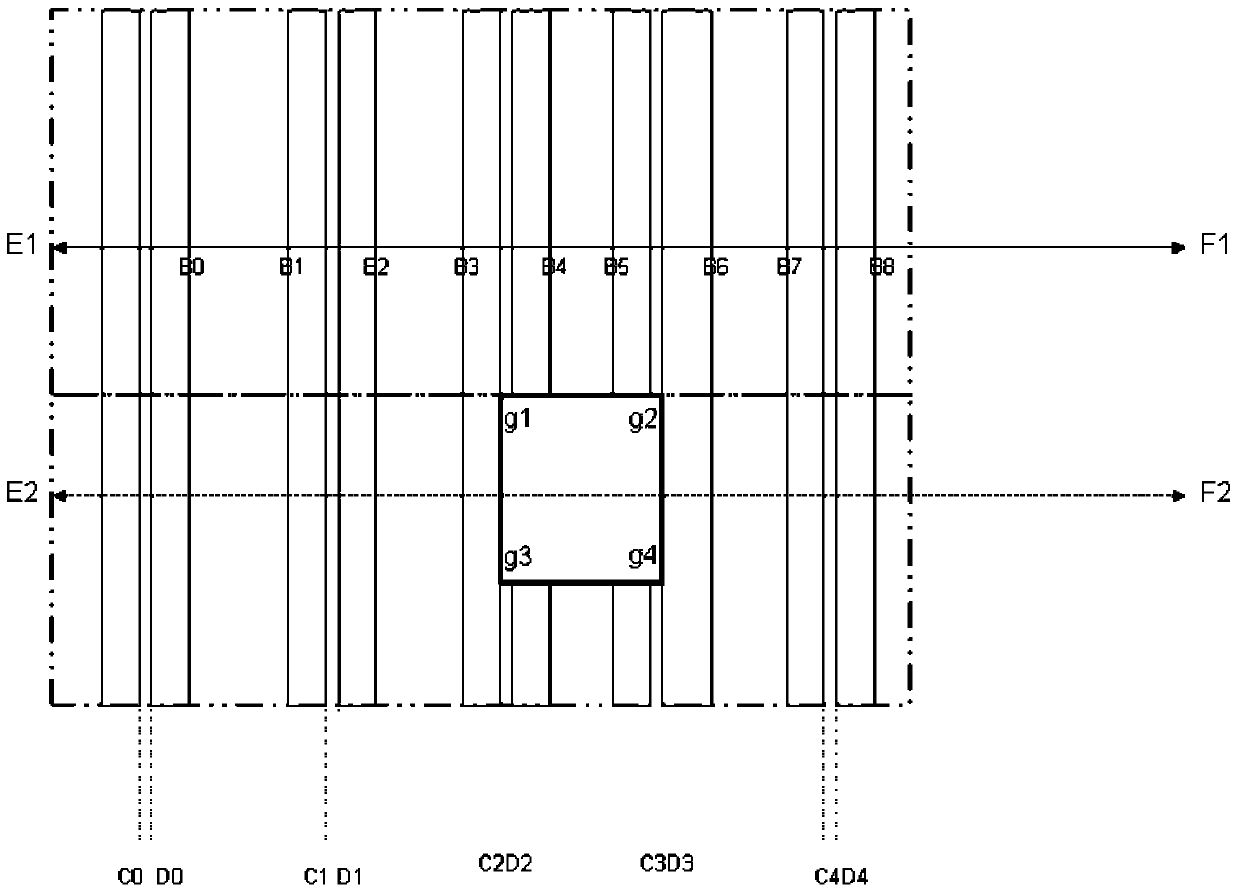

[0127] Such as figure 1 Shown is a top view of an existing power semiconductor device Figure one . In the top view, the embodiment of the present invention can be divided into zone 1, zone 2, and zone 3. Zone 1 is the current flow zone in the middle of the power semiconductor device. The current flow zone includes alternately arranged P-type regions 25 and N-type regions. The P-type region 25 is also the P-type region formed in the current flow region. The N-type thin layer, the N-type region is also the N-type thin layer formed in the current flow region; in the current flow region, the current will pass through the N-type region from the source to the drain through the channel, and the The P-type region 25 and the N-type region form a depletion region to withstand voltage in the reverse blocking state. Zone 2 and Zone 3 are the terminal protection structure area of the power semiconductor device. When the device is turned on, the terminal protection structure does not pro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com