Method for optimizing memory in 8051 chip

A memory and chip technology, applied in the field of memory optimization in 8051 chips, can solve problems such as occupancy and multiple memory, achieve the effects of optimizing memory, optimizing memory space, and improving work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

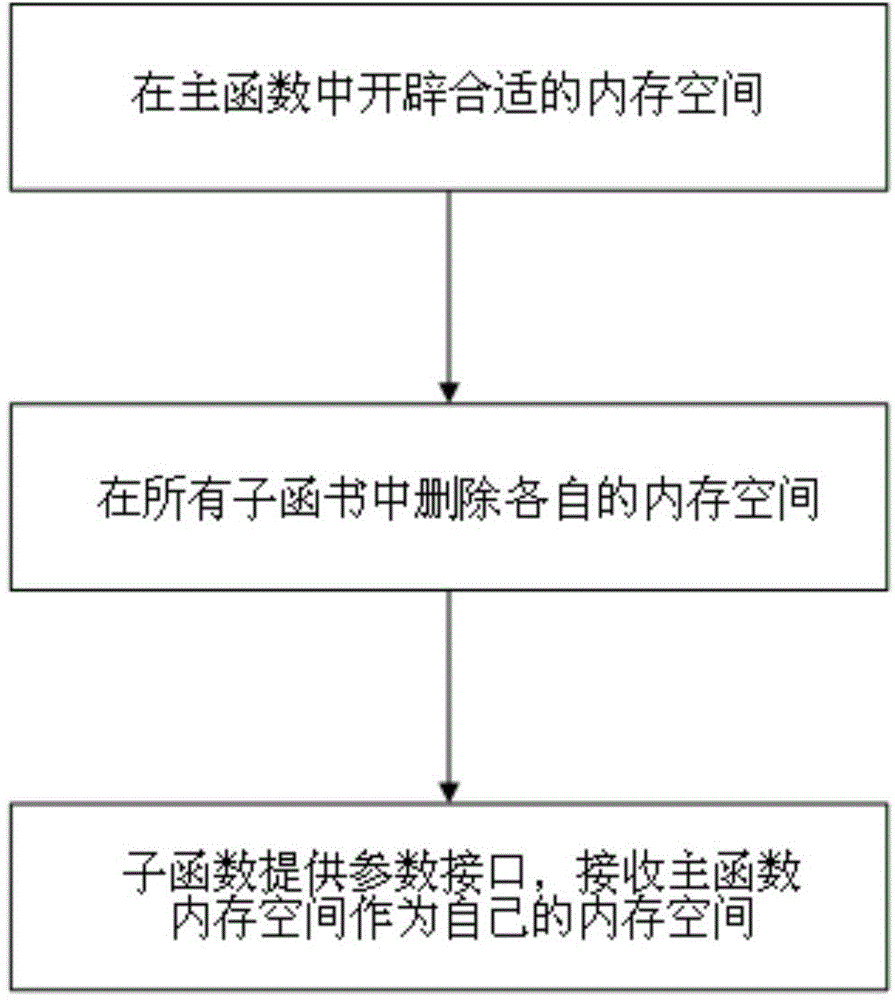

[0017] Below is an example of the present invention, demonstrates the usage of this invention by example. In this example, the c language under 8051 is used for explanation, combined with the drawings, the specific process is as follows:

[0018] The first step is to analyze the structure of the main function, find all the sub-functions called by this function, and calculate the memory usage in the sub-functions. Calculate the least common multiple of the sub-function with the largest memory usage and the memory consumption of the main function itself. Open up the memory space of this value size in the main function. If the sub-function calls other functions, use the sub-function as the main function, and use the method of the first step to calculate its memory usage.

[0019] The second step is to delete the memory space inside each sub-function.

[0020] The third step is to modify the interface of each sub-function, and allocate enough memory space for the sub-function t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com