Semiconductor structure and forming method thereof

A technology of semiconductor and gate structure, applied in the field of semiconductor structure and its formation, can solve the problems of improvement and limited improvement of parasitic capacitance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

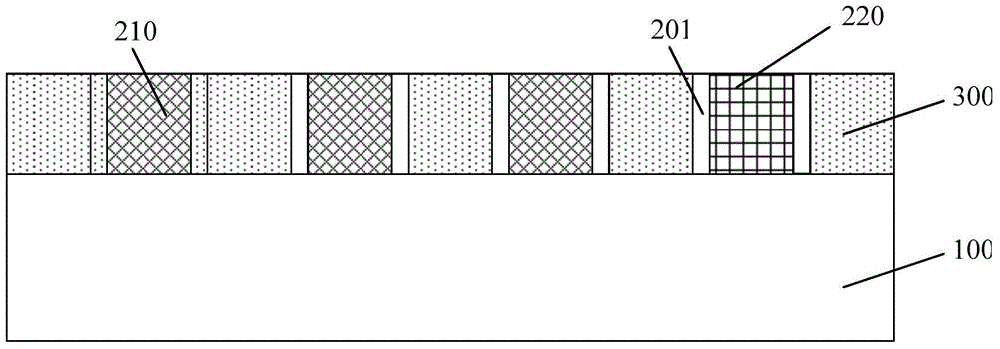

[0031] As mentioned in the background, there is high parasitic capacitance between the gates of transistors in the prior art, which affects the performance of transistors and circuits.

[0032] Although the existing technology can reduce the parasitic capacitance between adjacent gates by using low-K materials to form sidewalls on both sides of the gate, but due to the poor adhesion between the low-K material and the gate, the gate The quality of the sidewall formed on the sidewall surface is poor, and, as the process node continues to shrink, the difficulty of forming a sidewall of low-K material on the sidewall of the gate is further increased, thereby affecting the parasitic capacitance between the gates of the transistor The improvement effect is limited.

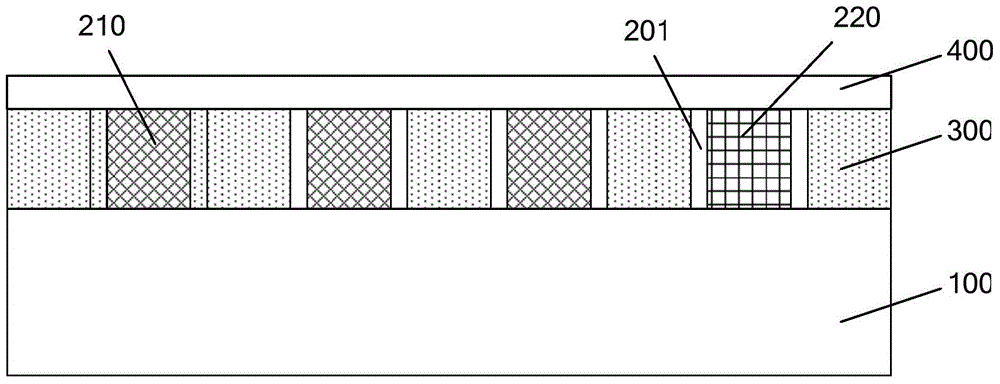

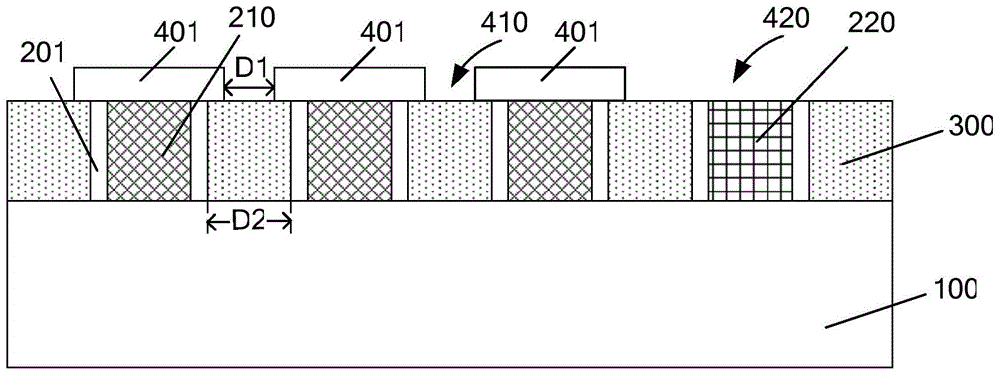

[0033] In the embodiment of the present invention, the parasitic capacitance between the gate structures is reduced by forming an air gap in the dielectric layer between the adjacent gate structures, thereby improving t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com