Wafer Level Packaging Method

A wafer-level packaging and substrate technology, applied in the manufacturing of electrical components, circuits, semiconductor/solid-state devices, etc., can solve problems such as unevenness, damage to the TSV and the back of the substrate, affecting the electrical signal of the TSV metal layer, etc. , to achieve the effect of good performance and good electrical signal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

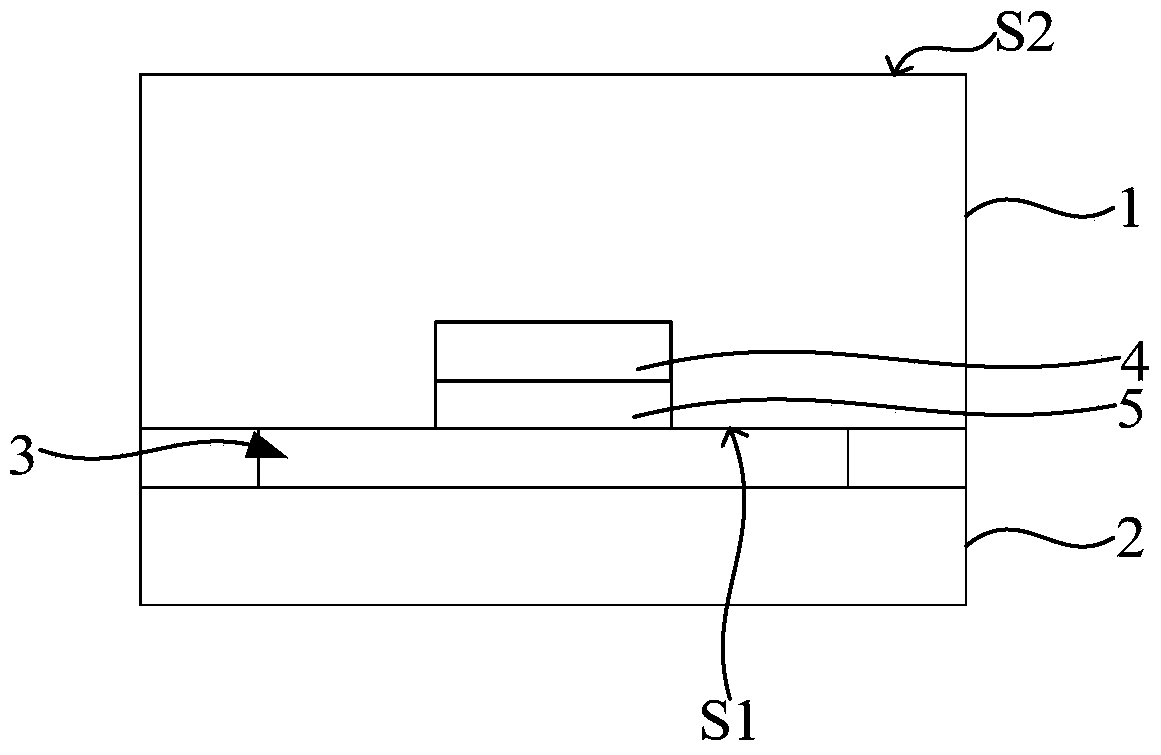

[0043] Aiming at the problems existing in the prior art, this technical solution proposes a new wafer-level packaging method. Using this wafer-level packaging method, after the first through hole is formed in the substrate, a relatively thin polymer layer is firstly formed on the back side of the substrate and the sidewall of the first through hole, and the polymer layer serves as the back side of the substrate and the sidewall of the first through hole. A protection layer for the sidewall of the through hole; then, etching the interlayer dielectric layer, and simultaneously etching and removing the polymer layer. Afterwards, the process of forming the polymer layer and etching the interlayer dielectric layer is repeated until the pad is exposed, and a second through hole is formed, and the second through hole is used as a silicon through hole.

[0044] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiment...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com