Array substrate motherboard, manufacturing method of array substrate motherboard and static electricity elimination device

A technology of an array substrate and a manufacturing method, which is applied in the field of an array substrate motherboard and its fabrication, and static elimination equipment, can solve problems such as affecting product quality, lead burning, and product yield decline.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

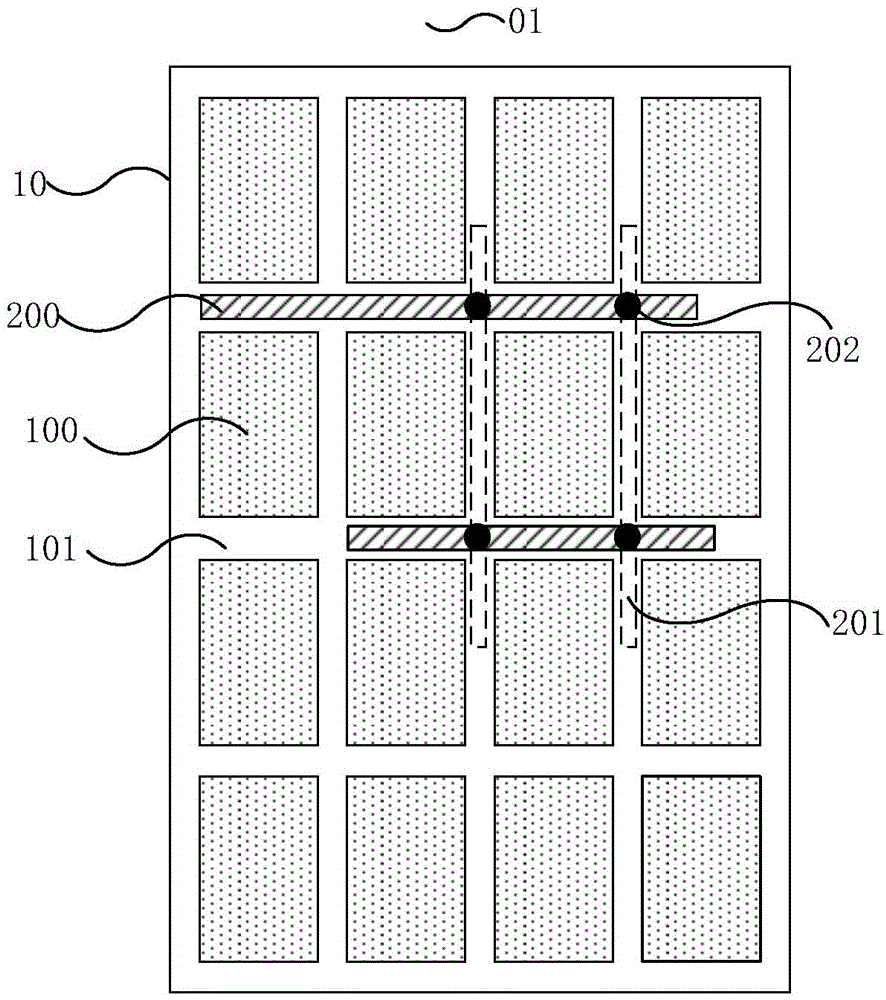

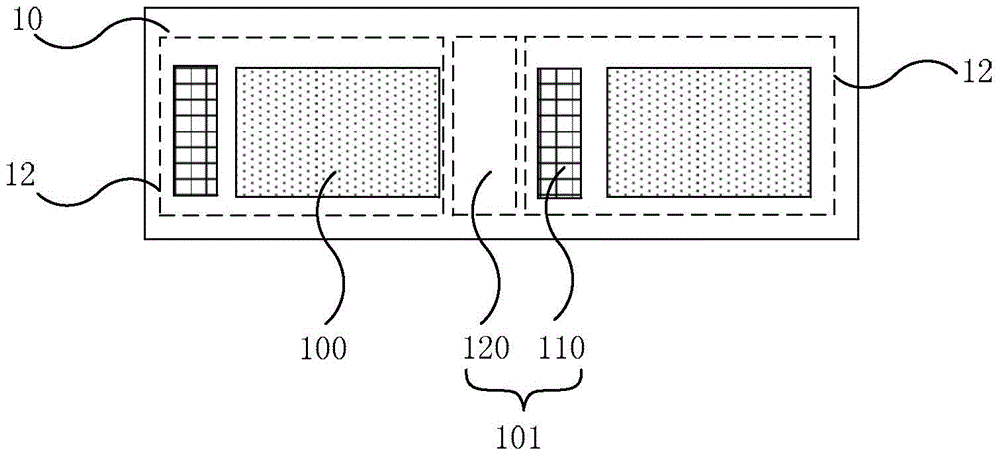

[0051] The non-display area 101 may include a binding area 110 and a gap area 120 between two adjacent display panels 12 , and the first wire 200 may be located in the gap area 120 .

[0052] Since the bonding area 110 is provided with a plurality of driving chips (gate driver 135 and source driver 134, etc.) interference, so the first wire 200 can be disposed in the gap region 120 . In addition, in the subsequent cutting process, the above-mentioned gap area 120 will be cut. If the line width of the first wire 200 is small, the first wire 200 arranged in the gap area 120 can be cut off together, so that the final There is no first wire 200 on the independent display panel 12 . This avoids signal interference caused by the existence of the first wire 200 during the display process of the display device.

[0053] In this case, the first wire 200 arranged in the gap area 120 can also be connected to the lead wire 13 in the binding area 110 or an electrostatic ring (not shown) ...

Embodiment 2

[0055] Since the size of the non-display area 101 between adjacent two display areas 100 is limited, in order to improve the effect of static electricity elimination, most of the space in the above-mentioned non-display area 101 can be covered by the first wire 200 to improve the first The contact area between the wire 200 and the rubbing cloth. However, if Figure 2a As shown, when the first conductive wire 200 with a certain line width is arranged obliquely in the above-mentioned non-display area 101 (the binding area 110 is omitted in the figure), it will not be able to cover most of the space in the non-display area 101 to the maximum extent. Therefore, if Figure 2b As shown, if the first wire 200 with a certain line width is arranged parallel to the 100 gate lines (or data lines) in the display area in the above-mentioned non-display area 101, it can occupy most of the space in the above-mentioned non-display area 101 , increase the contact area between the first wire ...

Embodiment 3

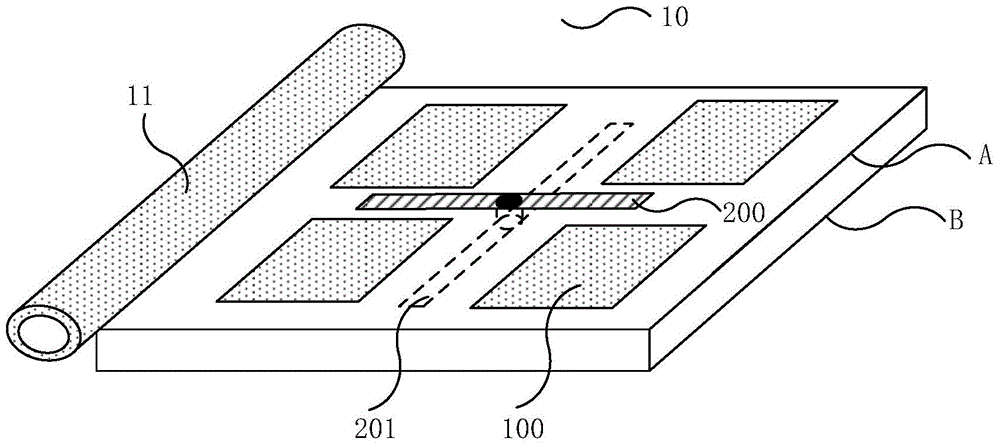

[0062] In the case that the non-display area 101 may include a bonding area 110 and a gap area 120 between two adjacent display panels 12, at least one lead wire 13 connected to a gate line or a data line in the binding area 110 as the first wire 200.

[0063] In this way, for the array substrate mother board 01 without the gap region 120 in the zero cutting process, the elimination of frictional static electricity can also be achieved. Specifically, the lead wire 13 in the bonding area 110 is used as the first wire 200, and the lead wire 13 is connected to the second wire 201 provided on the lower surface B of the array substrate mother board 01 through the through hole 202, so that in the rubbing alignment process, When the lead wire 13 is in contact with the rubbing cloth, the generated frictional static electricity can be released through the second wire 201 .

[0064] For any one of the above embodiments, the line width range of the first wire 200 is less than or equal t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com